HPI接口在脑电数据采集系统中的实现

时间:08-06

来源:微计算机信息

点击:

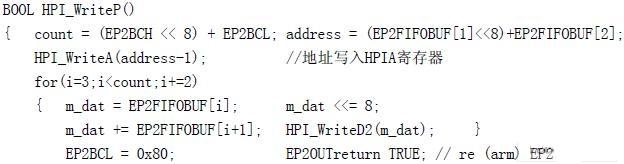

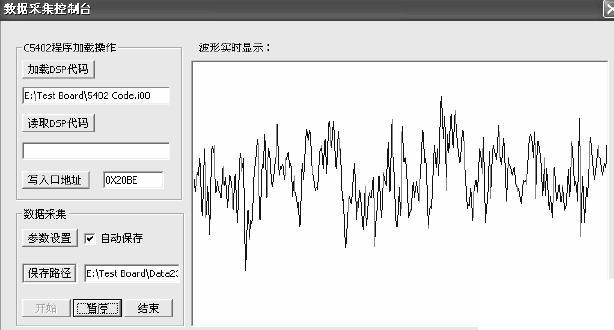

5 结 论 利用 C54x 的HPI 接口在脑电数据采集系统中的设计与实现,可用于自发脑电信号实时准确的高速采集。如从DSP 的实际应用环境出发,利用DSP 的HPI 加载方式和JTAG 调试相结合的开发模式,可以在线调试该电路板的制作,自行编制相应的主机软件,设计DSP KERNEI和HPI 接口逻辑,还可以实现开发基于HPI 自举和通信的DSP 应用设计方案。这样做可以缩短开发周期,且硬件资源透明。该透明化开发过程更利于学习者理解和掌握DSP 的软硬件原理。该方案还可以从脑电采集系统设计推广到其它领域。 本文作者创新点:在于将USB接口芯片CY7C68013A(100引脚)的在线仿真和DSP芯片TMS320VC5402的JTAG仿真结合起来,设计VC5402基于USB2.0和HPI自举加载的脑电采集系统。通过CCS5000集成环境,能即刻查看DSP内部HPI加载代码,使该方案设计的采集系统直观地调试并缩短开发时间。该方案还可以从脑电采集系统设计方面推广到其它领域。 |