基于FPGA的DES、3DES硬件加密技术

时间:06-18

来源:21IC

点击:

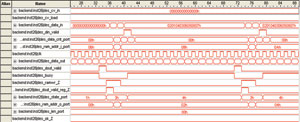

图4 3DES时序波形图 |

图5 DES时序波形图 注意事项 用SignalTap进行调试的过程中,要使采样频率大于被测信号的最高频率,否则无法正确反映被测信号的波形变化。由于系统的输入最高频率为50MHz,为了调试正确,利用了FPGA的锁相环对输入时钟进行倍频,从而用100MHz的信号作为采样频率。另外需要设置合适的触发点及采样深度。 系统优缺点分析及改进方法 优点:设计过程中采用了状态机和流水线技术,提高了数据的加解密速度;另外采用FPGA使得设计比较灵活,各模块均用了硬件描述语言编码实现。 不足之处:DES曾被人利用网络计算采用穷举攻击的方法破解过,目前也已经设计出采用穷举攻击在4小时内破解DES的机器。DES本身虽已不再安全,但在数据对安全性要求不高的场合仍然广泛使用着,其改进算法3DES的安全性还是相当强的。 系统改进方法:在要求安全性高的场合,可以采用安全性更高的算法(如AES等)来替换DES。 |

- 一种网络传输信息加密解密系统研制的方法(01-24)

- IE 7反钓鱼新功能 为可信赖网站开绿灯(01-05)

- 关于网络安全的几项关键性技术 (01-09)

- 3GPP LTE/SAE网络体系结构和标准化进展(04-14)

- 网络安全的七大误解(04-14)

- 无线局域网安全技术WPA (05-18)