基于DSP和USB的三维感应测井数据采集系统研究

时间:06-09

来源:世界电子元器件

点击:

|

图4 陷波器电路

A/D采样设计

TMS320F2812的ADC模块

TMS320F2812芯片中集成了一个12位A/D转换模块。为了满足系统多传感器的需求,F2812的A/D转换模块有16个通道,可配置为两个8通道模块,这样就形成了两个A/D转换器。在内部逻辑的控制下,用户可同时启动这两个或是其中某一个A/D转换模块。

F2812的ADC模块是嵌入式的,它与传统的A/D相比具有以下特点:A/D模块的硬件资源配置好了之后,用户可以用软件指令随时启动A/D采样,并获得A/D转换的结果。同传统A/D不同的是,采集功能单元的硬件资源配置还有一部分是通过软件完成的。

在TMS320F2812芯片中,A/D转换单元的模拟电路包括前向模拟多路开关(MUX)、采样/保持(S/H)电路、A/D转换内核以及其他模拟辅助电路。A/D转换单元的数字电路包括可编程转换序列器、结果寄存器、与模拟电路的接口等。图5为ADC模块的构成框图。

|

图5 ADC模块构成框图

ADC模块功能包括:

1)内置双采样/保持(S/H)的12位A/D转换模块,模拟输入为0-3V。

2)同时或顺序采样模式。

3)快速转换时间,可运行在25MHz的数模转换时钟或12.5MSPS。

4)多输入通道达16通道。

5)自动排序能力。一次可执行多达16通道的"自动抓换"。

6)两个独立的可选择8个模拟通道的排序器(SEQ1和SEQ2)可独立工作于双排序器模式,或级联后工作在可选择16个模拟转换通道的排序器模式。

7)可分别访问的16个结果寄存器用来保存转换结果。

输入模拟电压转换为数字值可由下式得到:

其中,ADCLO是A/D转换低电压参考值。

8)使用多个触发信号启动数模转换(SOC),比如:

? S/W:软件立即启动。

? EVA:时间管理器EVA(在EVA中有多个时间源可以启动转换)。

? EVB:时间管理器EVA(在EVB中有多个时间源可以启动转换)。

9)在双排序模式下,EVA和EVB触发器可各自独立的出发SEQ1和SEQ2。

10)中断控制方式灵活,可在每次转换结束或每隔一次转换结束发出中断。

数据采集系统A/D采样设计

本系统信号输入设计为24路。DSP本身的A/D输入通道是16路,所以要外接多路模拟转换器进行扩展。在电路设计中,使用3条DSP的A/D输入通道ADCINA0- ADCINA2,每一通道挂接一片8输入1输出多路模拟转换器4051,这样就可以扩展为24路模拟信号输入。为了减小信号通道之间切换带来的串扰,需在通道切换后加放大器减小信号输入阻抗,为了减小A/D转换产生的误差,用两路己知信号电平输入引入信号参考,提高采集精度。图6展示了TMS320F2812内嵌的A/D转换模块与输入信号之间的接口。

|

图6 A/D模块与信号接口

对于每一个转换,CONVxx位确定采样和转换的外部模拟量引脚。使用顺序采样模式时,CONVxx的4位都用来确定输入引脚,最高位确定采用哪个采样并保持缓冲器,其他3位定义偏移量。例如,如果CONVxx的值是0001b,ADCINA1就被选为输入引脚。如果CONVxx的值是1111b,ADCINB7被选为输入引脚 。

TMS320F2812 ADC的精度校正

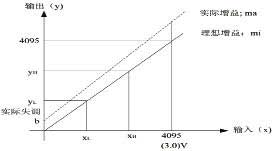

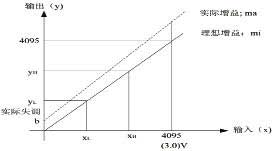

理想情况下,F2812的ADC模块转换方程为y =x ? mi,x=输入电压×4095/3,y为输出计数值。在实际中,ADC的误差不可避免,定义有增益误差和失调误差的转换方程为y=x ? ma±b,式中ma为实际增益,b为失调误差。F2812的ADC理想状态与实际转换精度较差的主要原因是存在增益误差和失调误差,因此必须对这两种误差进行补偿。校正方法如下:选用ADC的任意两个通道作为参考输入通道,分别提供给它们已知的直流参考电压作为输入(两个电压不能相同),通过读取相应的结果寄存器获取转换值,求得校正增益和校正失调,再利用这两个值对其他通道的转换数据进行补偿,从而提高了ADC模块转换的精准度。图7显示了如何利用方程获取ADC的校正增益和校正失调。

|  图7 理想转换与实际ADC转换

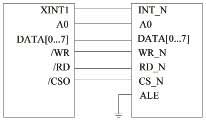

TMS320F2812与PDIUSBD12接口设计

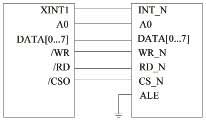

TMS320F2812与PDIUSBD12之间采用并口连接方式,并且都工作在3V电压下,给PDIUSBD12分配一个片选,可以通过读写地址对其进行操作,它们之间的电气连接不需要特殊处理,按照管脚功能一一对应连接即可。图8是TMS320F2812与PDIUSBD12的硬件连接图。

|  图8 TMS320F2812与PDIUSBD12的硬件连接图

系统软件设计

该数据采集系统可以通过USB接口直接与PC机相连,在CCS集成开发环境下通过JTAG接口来调试、烧写程序,可使用C语言来实现。

| | | | |