铁电存储器工作原理和器件结构

时间:05-22

来源:电子与封装

点击:

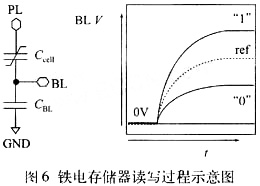

根据内存单元的极性状态,电荷电量小则为"0",电荷电量大则为"1"。这个电荷转化为一个读出电压,小于参考电压则为"0",大于参考电压则为"1"。由此读出所存储的信息,见图6。

进行读操作时,升高字线电压使MOS管导通,再使驱动线电压升高为VCC,从而存储电容的不同电荷将部分分配到位线寄生电容中去,于是BL上呈现出不同的电压,从而鉴别出数据。进行写操作时,升高字线使MOS管导通,驱动线加一脉冲,从而将位线上不同数据存入铁电电容的两个不同稳态。

通过加一个正电压或者一个负电压,这两种电压能够使电容变成两个不同的极性,通过这种方式把信息写入内存中。

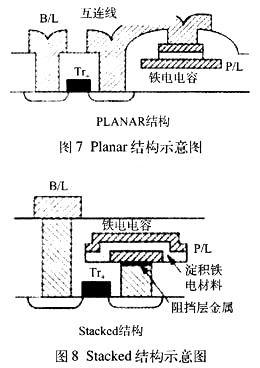

目前铁电存储器最常见的器件结构是Planar(平面式)和Stack(堆叠式)结构,两者的区别住干铁电电容的位置还有电容与MOS管互连的方式。在Planar结构中,将电容置于场氧上面,通过金属铝,将电容上电极和MOS管有源区相连,工艺相对简单,但单元面积较大;而在Stack结构中,将电容置于有源区,通过塞子(Plug)将电容下电极和MOS管源端相连,需要CMP工艺,集成密度较高。另外,Stack结构可以采用铁电电容制作在金属线上的做法,从而减少铁电电容在形成过程中对工艺的相互影响。两种结构示意图如图7和图8所示。

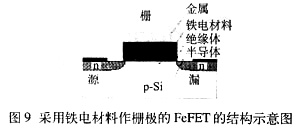

除此之外,还有一种结构,是采用铁电材料作栅极,这样的器件能够完全消除读出的破坏性问题,而且从理论上来说也更加节约面积,能够实现更大的集成度。但是这种结构目前还存在很严重的问题,数据保存能力很差,目前报道的最好的数据保存能力也只有一个月而已,所以距离实用还很遥远。图9是这种结构的示意图。

目前铁电存储器的线宽在0.5μm以上的时候一般都采用Planar结构,在0.5μm以下的时候一般都采用Stack结构。

7 总结

铁电存储器是新兴的非易失性存储器,它的起步比较早,率先实现了产业化,由于其具有功耗小、读写速度快、抗辐照能力强的优点,在一些需要快速存取、低功耗和抗辐照的小规模存储领域有市场。但是铁电存储器也存在集成度提高比较困难、工艺沾污较为严重、难以和传统CMOS工艺相互兼容的缺点,有待进一步研究解决。

- 电子熔丝在计算机应用中的优势(06-08)

- 卓联 Marvell?联手展示网络同步Ethernet解决方案(01-07)

- 恩智浦半导体发布USB收发器(02-23)

- 安森美扩充电源计算产品系列 推出新双缘多相控制器(03-13)

- ST推出测试65nm多标准硬盘驱动器物理层IP模块(04-08)

- ST测试65nm多标准硬盘驱动器物理层IP模块 (04-14)