基于RISC架构的龙芯处理器

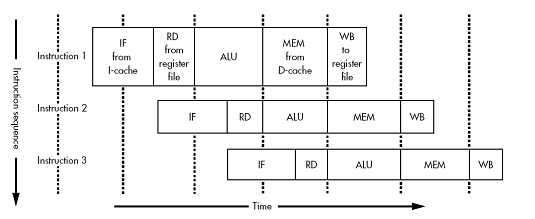

MIPS的五级流水线:分别是取指令(IF)、读CPU寄存器(RD)、算数逻辑运算(ALU)、读写数据缓存(MEM)、写回(WB)。

CSIC向RISC过渡

提到RISC必然会提到CISC。只有对CISC和RISC进行比较,才会明白为什么RISC终将取代CISC,为什么RISC前途光明,道路曲折。

CISC的典型代表是曾经在个人PC市场几乎处于垄断地位的奔腾系列处理器,以及现在流行的酷睿2双核处理器、AMD64位双核处理器等。运用在Intel IA32架构的x86指令集就是一个CISC指令集,而应用在Intel酷睿系列处理器上的EM64T架构,虽然取消了一部分x86的复杂指令,运用流水线技术、高速指令+数据缓存等一些RISC的执行手段来提高处理器的性能,但其本质上还是属于CISC架构。

Intel的EM64T架构不直接使用RISC架构的原因是:一方面采用全新的RISC指令集和RISC架构需要耗费大量的人力、财力和时间投入到研发部门,而且要承担巨大的风险,Intel在这一领域还"不专业";另一方面,微软Windows操作系统是基于x86指令集的,它不支持RISC。即使RISC处理器使用了微指令的手段,可以运行Windows操作系统,其性能也要大打折扣。(这也是为什么基于RISC指令集的龙芯处理器不能运行Windows操作系统的原因。)Intel为了保持和微软的战略同盟,也由于CISC不但还没有到寿终正寝的一天,反而发展到了其辉煌的顶峰,所以并没有将处理器架构进行本质的变革。但是从中可以发现,个人电脑处理器正在逐步从CISC向RISC过渡。毕竟RISC已经成为现今处理器发展的趋势。基于RISC指令集的Ubuntu7.10操作系统,由于其优越的性能和图形界面、完全免费、几乎不会受到病毒和木马的攻击等特性,越来越受到大众的欢迎。相信在不久的将来,微软也会推出基于RISC指令集的Windows操作系统,到那时,通用计算机处理器也将成为RISC家族的一员。

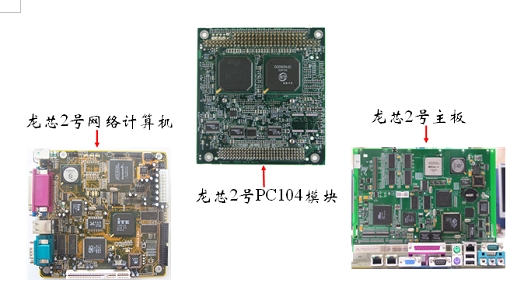

基于RISC架构的龙芯处理器

由此看来,发展我国自主知识产权的RISC处理器是相当重要的。龙芯处理器从无到有只用了短暂的几年时间,就达到了国外处理器行业几十年才达到的技术水平。虽然从总体上来说,龙芯处理器的性能还无法和Intel、ARM这样的国际先进企业的处理器系列相抗衡,但是龙芯处理器的设计理念始终走在处理器技术发展的前沿。

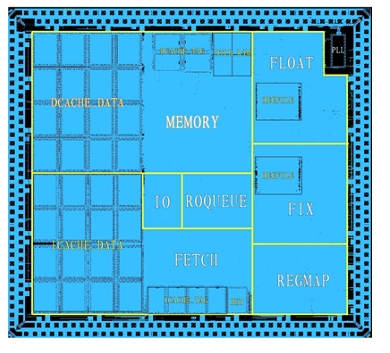

2002年龙芯一号处理器问世时,频率只有200~266MHz,只能应用在低端嵌入式领域。最新问世的龙芯2F处理器,主频达到1.2GHz,相当于奔腾4处理器。龙芯2F是一款64位、四发射、乱序执行的RISC处理器,采用MIPS III指令集。该处理器采用先进的乱序执行技术(如寄存器重命名、转移预测和动态调度)和Cache技术(如非阻塞Cache、load猜测、动态内存相关和写合并技术),并集成片上二级Cache、DDR2内存控制器和I/O控制器,来提高流水线效率和I/O能力。

龙芯2F已经是一款有较强竞争力的CPU芯片产品,与龙芯2E相比,主要有以下几个方面的提高:1. 主频提高30%以上,通过频率筛选,将有1GHz以上的产品;2. 相同频率下功耗降低40%左右,并增加了很多诸如降频、温度传感器、关闭L2等功耗管理功能;3. 集成了更多的系统功能,除了CPU外,还集成了DDR2内存控制器、66MHz PCI/100MHz PCIX控制器、Local IO控制器、GPIO、中断控制器、DMA控制器、部分显示加速等功能,将大幅度降低系统成本;4. 封装更小,龙芯2E的封装为35×35mm,龙芯2F为27×27mm;5. 可测性设计(DFT)和可生产性设计(DFM)有明显提高,可以降低芯片成本。