基于USB2.0的高速数据通信接口设计

1 CY7C68013结构特点

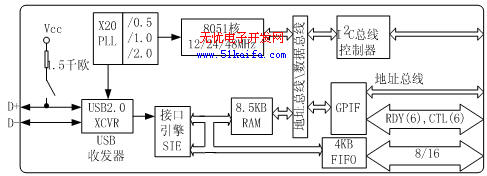

CY7C68013是Cypress公司研制开发的EZ-USB FX2系列芯片,该芯片符合USB2.0规范,同时兼容USB1.0的全速工作模式[2],它的功能框图主要包括5个部分(图1):

(1)收发器。USB和PC机通过D+和D-两根信号线进行数据传输,数据以480Mbit/s的全速信号或者以240Mbit/s的半速信号在D+和D-信号线上差分传输。

(2)智能接口引擎(SIE)。SIE通过包排序、信号产生、信号检测、CRC产生、CRC校验、NRZI数据编码、位填充、包标识产生和解码等功能来处理USB通信协议,并保证传送到USB电缆上的数据字节以LSB开头。

(3)通用微控制器以及片上RAM。USB控制器采用通用的8051微控制器,即编程语言为51系列单片机的通用语言,可使实际操作更加灵活方便。

(4)I2C总线控制器。主要为完成将USB控制器作为主设备时必须的配置。

(5)片内FIFO。其容量为4KB,可以快速实现与不同速度的外设通信。

2 CY7C68013与TMS320C6203B的接口电路设计

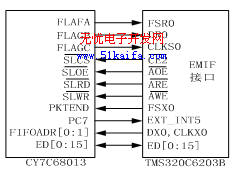

CY7C68013是一个非常方便的USB2.0实现方案,它提供与DSP连接的接口,连接方式有两种:Slave FIFOs和Master可编程接口GPIF[3]。本文采用Slave FIFOs异步读写方式。Slave FIFOs方式是从机方式,DSP可以象读写普通FIFO一样对CY7C68013内部的多层缓冲进行读写。具体的电路连接如图2所示:

图1 CY7C68013功能框图

图2 CY7C68013与TMS320C6203B电路连接图

FLAGA、FLAGB和FLAGC是CY7C68013内部FIFO的状态标志,TMS320C6203B通过通用I/O口获得CY7C68013内部FIFO的空、半满(由用户设定半满阈值)和满这3个状态信号,EMIF接口的CE2空间对CY7C68013进行读写操作。其工作过程为:DSP通过USB向PC发送数据时,首先查看空、半满和满这3个状态信号,然后向USB写入适当大小的数据,以保证数据不会溢出;PC机通过USB向DSP发送命令字时,USB通过中断方式通知DSP读取命令字。

3 软件设计

系统的软件设计包括3部分:C8051固件设计、设备驱动程序没计和应用软件设计。CY7C68013的功能具体实现过程如下:

(1)当设备连接时,Windows的设备管理器自动检测到该设备,并读取由CY7C68013核心(并非C805l固件)传回的设备描述符,根据它提供的厂商和产品ID号VID/PID(存放在FX2外接E2PROM中)与.inf文件进行比较,找到固件下载驱动程序(ezloader.sys),从主机将C8051固件下载到CY7C68013的RAM中。

(2)C8051固件下载到RAM后,CY7C68013仿真一个脱离再连接至USB总线的过程,执行重新枚举过程,让C805l固件控制USB传输。Windows的设备管理器会检测到新的USB设备的连接,并根据C8051固件提供的厂商ID(VID)/产品ID(PID)(不同于CY7C68013核心提供的VID/PID)来加载该USB设备的设备驱动程序。

(3)应用软件调用CreateFile()API函数,使用识别该设备的符号链接来取得该设备的代号。取得设备的句柄后,应用软件通过DeviceIoControl()向I/O系统服务发出要求传入数据的I/O请求,I/O管理器将此请求构造成一个合适的IRP传递给CY7C68013设备驱动程序。CY7C68013设备驱动程序根据该IRP中包含的具体操作来构造相应的USB请求块,并据此形成新的IRP传递给USB总线驱动程序。USB总线驱动程序根据该USB请求块从CY7C68013设备读取数据。操作的结果再用IRP一层一层地返回给应用程序,应用程序再对数据进行分析和处理[4]。

3.1 C8051固件设计

Cypress公司为了简化固件开发,缩短时间,加速USB外围的开发,在EZ-USB FX2软件开发包里提供了固件架构。该固件架构利用C8051的程序代码来实现CY7C68013芯片起始设置、USB标准设备请求的处理以及USB闲置模式的电源管理服务。用户仅需提供其USB描述符表(即dscr.a51)及实现外围功能的程序代码(periph.c),即可完成完全兼容的USB设备。

固件的编译在Kei的集成开发环境中进行,在建立的项目中包含5个文件ez_usb.lib、

usbjmptb.obj、dscr.a51和periph.c,其中:

固件架构程序流程如图3所示。该程序首先初始化所有的内部状态变量,然后调用TD_Init函数进行初始化,初始化主要包括:

(1)使CY7C68013工作于异步从FIFO模式。相应的寄存器操作为IFCONFIG=0xCB。

(2)将4KB的FIFO对应到两个端点(EndPoint),即EndPoint2和EndPoint6。相应的寄存器操作为:EP2(:FG=0xA0,EP6(:FG=0xE2。EndPoint2与EndPoint6分别对应21kB的内部FIFO(下面分别称作FIF02,FIF06),存放LJSB需要上传与接收的数据。其中EndPoint2为OUT型,负责从主机接收数据;EndPoint6为IN型,负责向主机发送数据。另外EndPoint2

与EndPoint6均采用批量(BULK)传输方式,这种方式相对于其他LJSB2.0定义的传输方式

具有数据可靠、传输速率高等特点,是最常用的传输方式。www.51kaifa.com/

(3)对FIF0进行配置。相应的寄存器操作为E192FIFO(:FG=0xl 1,EP6FIFOCFG=0x0D。本案例将FIF02,FIF06设置成自动方式。

- 局域网与广域网的接口标准 (01-09)

- 用AMBE-1000实现的语音分组技术(01-10)

- R4网络接口和电路域容灾技术(01-05)

- 如何辨别优劣网卡(03-02)

- 八种固定WiMAX接入方案(03-12)

- Cu接口标准化介绍(02-14)