一种基于SoC应用的Rail-to-Rail运算放大器IP核

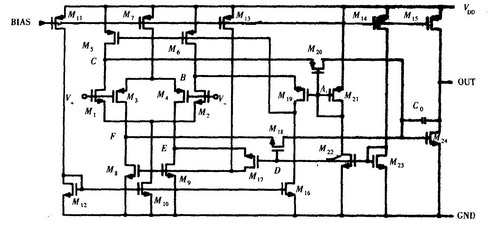

图3 Rail-to-Rail 运算放大器结构

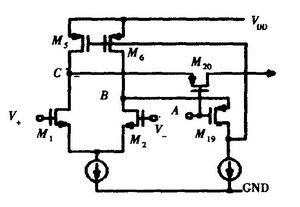

图4 阻抗变化机理图

2 仿真结果与讨论

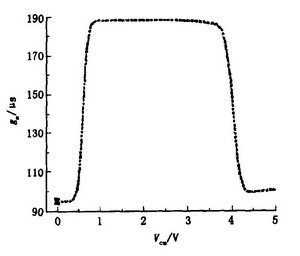

电路采用上华0.6μm DPDM CMOS工艺,基于BSIM3V3 Spice模型,用Hspice进行仿真. 电源电压为5V ,偏置电压为3. 7V. 输入级的跨导随输入共模电压变化的结果如图5 所示. 输入级跨导变化两倍,跨导在0.8V到3.85V之间恒定,为190μs. 跨导变化是因为输入共模电压在中间值时,输入级跨导为NMOS和PMOS输入对跨导之和,而在共模电压接近GND或VDD时,输入级跨导分别为PMOS和NMOS输入对的跨导.

图5 输入级跨导曲线图

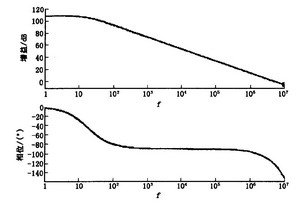

将运放接成电压跟随器的形式,测量其单位增益响应,仿真结果如图6所示. 从图6 可以看出,放大器的输入输出达到了整个电源电压范围.运算放大器的幅频、相频特性如图7所示,整个电路的直流开环增益达107.8dB ,相位裕度为62.4°,单位增益带宽为4.3MHz.

图6 单位增益传输特性曲线

图7 运算放大器幅频、相频特性

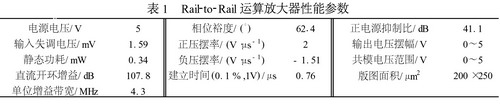

整个运算放大器的设计结果如表1所示. 运算放大器的整体性能比较好,并且在5V的电源电压下,功耗只为0.34mW. 此外,运放的对称性好,结构紧凑,版图面积小,只为0.05mm2 ,非常适合SoC的应用.

3 总 结

从IP核设计的角度出发,笔者设计了一种结构简单、低功耗、高增益的Rail-to-Rail CMOS运算放大器.输入级采用互补差分对结构,输出采用分压电路进行求和,再接以PMOS为负载的共源级进行放大. 较以往的Rail-to-Rail运算放大器大大简化了结构,对称性好,版图面积小,易于实现. 模拟结果表明运放的输入输出都达到全摆幅,且增益和相位裕度分别为107.8 dB和62.4°,功耗只为0.38mW,非常适于做成SoC的IP核.

- 统一功率格式降低SoC的功耗(05-28)

- 第三方IP:SoC设计的一种不稳固基础(09-15)

- 赛普拉斯智能照明解决方案支持欧司朗 DRAGON LED 以精简照明设计流程(11-26)

- 基于改进的遗传算法软硬件划分方法研究(07-20)

- 锂电池均衡处理技术解决SOC和C/E失配问题(06-28)

- PSoC3应用于多通讯接口时的DMA设计 (03-05)