适用于高速高精度流水线ADC的放大器

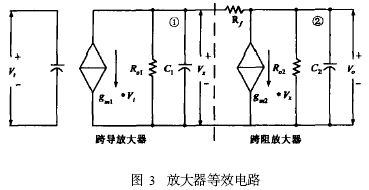

,它分别连接于共源放大器的输入和输出端,形成电压并联负反馈,降低该级的输入输出电阻;gm1、gm2则分别为管M1、M2的跨导。由于Ro1、Ro2均为很大的电阻(远大于1/gm1或1/gm2),其影响可以忽略不计。需要特别指出的是,该电路的设计必须满足C1≤C2(实际电路中一般都很容易满足该条件),下面的讨论都是在这个前提条件下进行的。

根据基尔霍夫电流定律列方程:

gm1Vi+VxsC1+(Vx-V0)/Rf=0(1)

gm2Vx+V0sC2+(V0-Vx)/Rf=0(2)

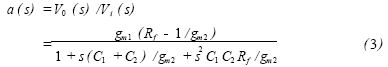

解方程组得:

由传输函数看出,该放大器可以等效为一二阶系统,其直流增益为:

A=gm1(Rf-1/gm2)(4)

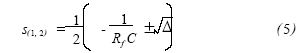

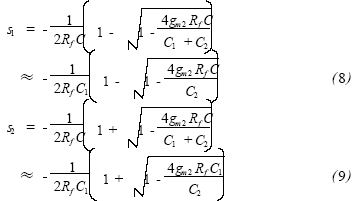

它的极点就是方程1+s(C1+C2)/gm2+s2C1C2Rf/gm2=0的根,值为:

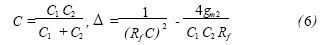

其中,

因为C2≥C1

所以,C≈C1,C1+C2≈C2(7)

当Δ≥0即C1+C2≥gm2RfC时,方程有两实根,即放大器有两个实极点

由式(8)、(9)看出,随着C2的增加极点s1的绝对值显著减小,即极点频率随C2的增大而降低,这不利于放大器的稳定。

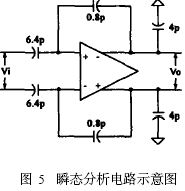

当C1+C2<gm2RfC时,方程有两个共厄复根,即放大器存在一对共厄复极点,它们的实部为:

公式(10)表明,共厄极点的实部取决于C1,几乎不受C2值的影响。合理的电路设计可以保证C1是一个很小的值,从而使整个电路的极点位于很高的频率。

由上面的分析可以得到以下结论:当C1≤C2,并且C1+C2<gm2RfC时,图2所示放大器的极点几乎不受输出端负载电容的影响,而取决于内部节点的电容;由于该内部节点电容值可以控制到很小,从而保证极点位于很高的频率,有效的解决了引言中提到的问题。

模拟结果

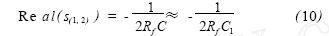

利用我们所提出的预放大电路,设计了图4所示的运算放大器。它是两级结构,前级为预放大电路,后级为套桶式放大器。

若需要更高的直流增益或者较大的输出电压摆幅,图中所示单级放大器可以采用增益自举放大器。

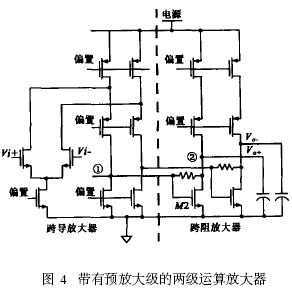

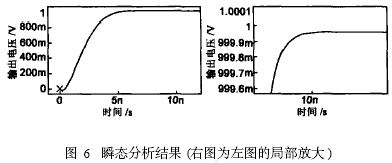

该两极运算放大器用于实现8倍的闭环增益,用0.35μmCMOS工艺模型在Spice中进行模拟,模拟的电路示意图见图5。当输入为0.125V的阶跃信号时,Hspice瞬态分析的结果如图6所示:

由模拟结果得到运算放大器的各种参数值如表1所示:

若去掉预放大级而仅仅采用后面的单级放大器,即使将输入管的尺寸加倍,也需要高达80mW的功耗。并且增大输入管的尺寸会使放大器的输入端寄生电容增加,而应用于流水线ADC中时,该电容会影响ADC的各项性能。

与单级放大器相比,图4所示电路还有一个突出的优点:输入共模范围大。当然单级电路也可以采用折叠共源共栅结构来增加输入共模范围,但采用这种结构会使功耗大大增加。

对于预放大级,从Hspice的输出文件中提取各项参数代入(4),(10)中进行计算,计算结果与模拟结果对比如表2:

可以看到,理论计算值与实际模拟结果十分接近,证明了前面所做推导的正确性。

总结

本文介绍了一种适用于高速高精度流水线ADC的运算放大器,它是带有预放大级的两级结构。其中,用做预放大级的放大器是由我们特殊设计的,它在负载电容较大的情况下仍能达到很高的带宽,我们对它的传输函数进行了理论推导,模拟结果证实了推导结论的正确性。用0.35μmCMOS工艺所设计的该类型运算放大器在负载电容为4pf的情况下,实现了超过1GHz的增益带宽积,功耗仅为25mW,远低于同性能其他结构的放大器。

- 高速差分ADC驱动放大器AD8137及其应用(01-17)

- 8位高速A/D转换器TLC5510的应用(02-16)

- 一种高速低压低静态功耗欠压锁定电路(03-13)

- 高速串行接口特征与应用(05-20)

- 高速数字电路电源系统的电磁兼容研究(11-20)

- 数字式超声波探伤仪中高速数据采集模块设计(04-04)