高效率E类射频功率放大器

1 引言

作为发射器的最后一级,功率放大器供给负载所需要的、额定的不失真功率以控制负载工作,使得信号通过天线发送出去,同时减少误码。它不要求最大的功率放大倍数,而是要求获得最大的、不失真(或者失真但合乎要求)的输出功率。由于移动通信的普及,提高手机的功率效率、降低电源消耗、减小体积重量、延长通话时间成为开发移动电话急需解决的技术问题。在系统的功耗中发射机占了绝大部分,其末级的功率放大器又是最关键的部件,存在着较大的功率损耗。对于不同类型的发射机,末级功率放大器占整个系统功耗的60%~ 90%,制约了系统性能。因此,需要设计一种高效率功放,这对于常规的电子设备,例如中继通信站等,提高效率,降低电源损耗、降低维护成本也有重要的意义。

本文研究了一个用0.6μm CMOS工艺实现的功率放大器, E型功率放大器具有很高的效率,它工作在开关状态,电路结构简单,理想功率效率为 100%,适应于恒包络信号的放大,例如FM和GMSK等通信系统。

2 工作原理

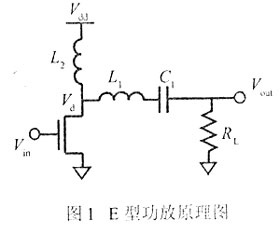

下面用图1所示的原理图进行说明E型功率放大器的工作机理。

|

|

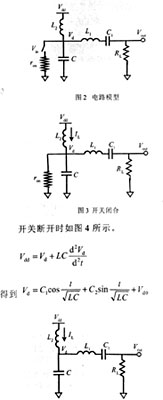

当输入电压Vin大于开启电压时,晶体管工作在可变电阻区,漏源之间有很小的电阻,假设为r on,这相当于开关闭合;如果输入电压V in小于开启电压时,MOS管处于截至状态,没有电流流过漏级,这相当开关断开,因此电路原型可以用图2所示的模型表示,电容 C为MOS管的结电容或者外接电容。当开关闭合时,如图3所示,有 Vdd-Vd=L(d IL/dt),由于ron 很小,所以Vd很小,近似为零。所以 Vdd≈L(dIL/d t),解之得到:lL≈(V dd/L)t+ IL0,IL0是电感电流的初始值,可以看出当开关闭合后电流随时间线性增长。

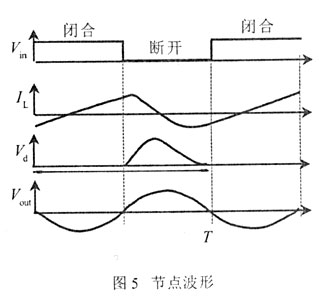

在开关闭合时,如果电容不能充分放电,就要损耗1/2×CVd2的能量,所以电容必须能够在输入电压变化的瞬间充分放电,也即当dVd /dt=0时,Vd=0。一个信号由无数个谐波分量组成,利用 L1和C1组成的滤波器从 Vd的各次谐波中选择等于输入电压频率的基波分量,这也就对信号进行了相位或者频率的调制,在功率放大以后传送到负载上。电路中的参数随输入变化的关系如图5 所示。

|

|

|

|

由于ron很小,所以在开关闭合的时候, ron上的电压远远小于电源电压V dd,它不会显著地影响输出回路中的电流,因此负载的输出功率基本上不受晶体管特性的影响。电路中每个节点的电压值都和电源的电压成正比,所以传送到负载上的功率也就和Vdd2成正比,同样 ron消耗的功率也和Vdd 2成正比,所以效率η=PRL / (Pron+PRL)在一定的范围内为一定值,同时通过调整电压可以保证一定的输出功率。

3 存在的问题及解决措施

虽然图1所示的电路在形式上简单,但是本身带有很多的问题。例如,作为开关使用的晶体管工作在可变电阻区,由于本身固有电阻 ron的存在,Ids= β[(Vgs-VT) Vds-(Vds2 /2)],0<Vds<Vgs -VT,Ids为漏极电流, Vgs是栅源电压,VT是器件的开启电压,β是MOS晶体管的跨导系数。其中β=( με/tox)(W/L); μ为沟道中电子的有效表面迁移率;ε是栅绝缘层的介电常数; tox是栅绝缘层的厚度;W是沟道宽度; L是沟道长度。为了减少电阻ron的损耗,它的宽长比要尽量的大。晶体管的输入电容C =εWL/tox一般都是通过感性负载耦合掉,超过一定的宽长比后,需要耦合的电感值就会太小,很难用CMOS工艺精确实现,而且大的栅漏电容 Cgd会引起输出端到输入端的强反馈,这导致了输入和输出之间的耦合。最后,单端输出电路每个周期都要向地或者硅衬底泄放一次大的电流,这可能会引起衬底耦合电流的频率和输入、输出信号的频率相同,从而在输出端产生了错误的信号?

3.1 差分结构

采用如图6的差分结构可以解决衬底耦合的影响。在差分结构中,输入端为差模电压。任意时刻,一个晶体管导通工作在可变电阻区,另一个工作在截止区,所以电流在一个周期中泄放到地或者衬底两次,由此而引起的耦合电流的频率为信号频率的两倍,这就消除了衬底耦合对信号的干扰。在同样的电源电压和输出功率条件下, Vd+只需为单端电压的1/2,因此通过差分结构中的每个晶体管的电流要比单端的小得多,所以在不增加开关消耗全部功率条件下,可以使用尺寸较小的开关晶体管。

- D类MOSFT在发射机射频功放中的应用(11-18)

- 单片射频收发芯片A7105的原理与应用(10-12)

- LDO电源管理模块的分析及其在数字模拟射频系统中的应用(01-26)

- 如何完善您的射频采样解决方案?(11-26)

- 核磁共振系统中射频开关设计(01-04)

- 基于MATLAB仪器控制工具箱的SAW标签阅读器系统设计(06-24)