石英晶振的电路组成设计与原理分析

时间:08-17

来源:互联网

点击:

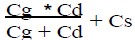

ODE ,可根据用户的需要选择合适的外形尺寸和封装的晶体。主要电性指标: FL 、ESR 的CLOCK需要选用FL 及公差,并按Cg/ Cd 值,计算而得CL = (Cs :线路分布杂散电容)

(Cs :线路分布杂散电容)

6 、ESR :单位Ω,工作温度范围的频率公差。

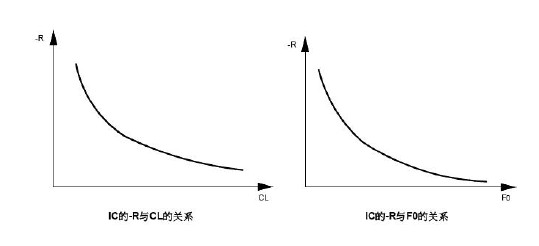

正确的选取Cg/ Cd 的值将有利于振荡电路的工作稳定,并能使振荡频率满足使用的CL K 要求。其选取的步骤如下:

(1) 首先应该按照- R 的需要选择Cg/ Cd ,在满足TS 的情况下应尽量小些,保持较高的- R 以保证振荡的稳定性。当无法满足- R 要求时应考虑对IC 的特性重新评价、选择。

(2) Rf 值选取:取用的XTAL 为基本波的时候,Rf选用1MΩ;3RD 模式的XTAL 时须考虑截止频率必须界于基频与3RD 的中间以保证3RD 工作正常为原则,通常Rf 阻值在2 - 15KΩ 间。

(3) 为了避免对XTAL 的过激励而影响电路的正常工作,建议采用Rr 以控制XTAL 的激励功率;其数值视频率高低可在33 - 68Ω间选取。

(4) 对于有EMI 要求的振荡电路设计中必须选取SEAM 焊封4PAD 的晶体谐振器,同时赋予合理接地方式,可满足EMI 防护的需求。

四、发展趋势

石英产品与其它的电子器件同样朝着轻薄短小演进。石英产品从1990 年开始朝着SMD 的方向发展,1998 年开始又向小型SMD 的方向发展,因此轻薄短小的竞争也就从此白热化起来。随着CPU 的运转速度的加快,石英谐振器和石英振荡器的高频化进程也在加快。在石英水晶的压电效应发展至今,将进入重要的频率控制组件发展的新纪元。

- 整流电路(11-30)

- 单运放构成的单稳延时电路(11-29)

- 直流稳压电源电路(11-30)

- 基于ISP1581型接口电路的USB2.0接口设计(01-18)

- 单电源供电的IGBT驱动电路在铁路辅助电源系统中的应用(01-16)

- 为太阳能灯供电的低损耗电路的设计(01-22)