一种高速脉冲峰值保持电路设计

时间:08-09

来源:互联网

点击:

4 实验结果

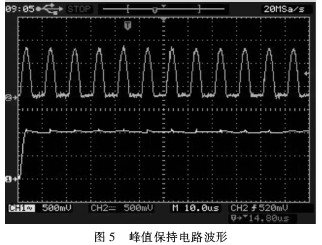

为验证文中电路的可行性,用盛谱科技公司的F05型任意波信号发生器产生幅度为1V、频率为100 kHz的脉冲信号作为输入,用同惠电子公司的TD01000型双通道示波器观察输入输出电压波形,如图5所示,波形1为峰值保持电路输入信号波形,波形2为峰值保持稳定后的信号波形。从图中可以看出,文中设计的峰值保持电路较好地保持了输入信号的峰值,起伏较小。电路保持住的峰值与输入信号峰值误差<1%,满足A/D转换的要求。

5 结束语

文中介绍了采用电压比较器LM311,采样/保持芯片LF398集成芯片等构成的峰值保持电路,结构简单、成本低廉、易于调试。实验表明,该电路性能可靠、稳定性好、可以有效地克服温漂,灵敏度好,误差小于<1%,可用于高速脉冲信号的峰值甄别保持,下一步将致力于提高电路在复杂环境下的峰值保持的有效性,提高电路的抗干扰能力。

- 正、负峰值保持电路原理分析(03-06)

- 单脉冲电压正向峰值保持电路及原理分析(03-05)

- 窄脉冲高速峰值保持电路及原理分析(03-05)

- 高性能CMOS集成电压比较器设计(10-07)

- 对数放大器在弱光检测中的应用(07-09)

- 9位100 MSPS流水线结构A/D转换器的设计(02-11)