实现双向闭锁箝位的一种新方法

与NPN双极性Qn1的集电极区域和PNP双极性Qp的基极区域相对应。在对称方向,原理图第二部分(包括虚线以下的Qn2)表示器件另一部分的等效电路(图1中未显示)。除了确定保护箝位特性的基本原理图之外,寄生PNP双极性Qparasitic的发射极、基极和集电极分别由p型区域、浮动式NBL (H-NW) 和P型基板中的p+有效区域构成。器件采用绝缘硅片工艺制造时,虽然不必考虑Qparasitic问题,但这还是常常会对保护箝位特性造成不良影响,并在大型BCD工艺中产生不必要的基板电流。当器件采用大型工艺制造时,两个箝位器件引脚的间距很近,这种效应会有所降低,从而形成高击穿隔离区域,增加与器件周围隔离保护环的间距,进而在有效纵向与横向PNP寄生双极性区域中产生低增益和高开路基极击穿。

三、保护箝位器件特性

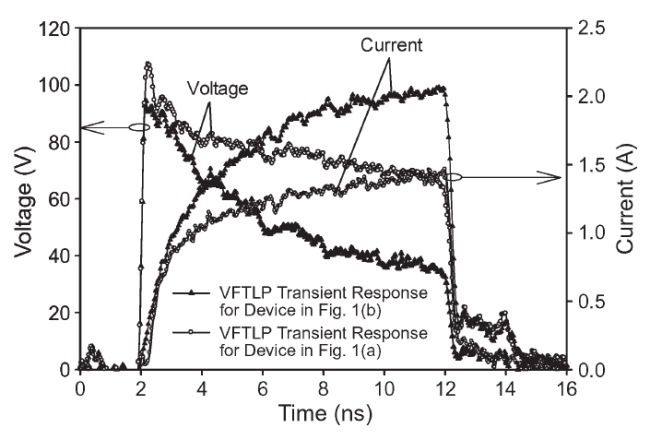

保护箝位器件根据电路I/O目标操作时的高压内核器件设计窗口和ESD与EMI应力条件仿真相应进行优化。图3显示优化后双向保护箝位器件产生的高应力下的电压与电流瞬态响应。箝位器件显示闭锁电压相似,但保持电压存在明显差异。这种差异源自对n+和p+有效区域"T"形及孤岛阵列结构的修改。

当PNP(图2中的Qp)空穴驱动动作占主导地位,即可实现针对BHEC箝位器件的高保持电压,无需改变两个箝位器件引脚的横向间距。另一方面,对BEEC箝位器件而言,响应时间更快的电子驱动NPN(图2中的Qn1)越来越占主导地位,会产生较低的保持电压,特别适合±25 V以下工作的应用。对BHEC而言,较大的p+有效区域"T"形可为增强空穴注入和PNP动作创造条件。类似地,对BEEC箝位器件而言,"T"形n+有效区域更大,在这种情况下,可以增强电子注入和NPN动作。高鲁棒性的双向器件结构通常具有低保持电压[3]、[4],"T"形和孤岛结构设计的目的是让器件保持高传导性调制,同时调整图2等效原理图中嵌入式双极的增益,以实现通态响应控制。

图3, 140 V极快TLP施加到受测器件时,图1(a)和图1(b)结构的电压与电流波形对比。

BHEC箝位器件通态保持电压高于BEEC箝位器件,因为它的发射极注入效率较低、基极瞬态时间较长、空穴载荷子移动性较低,由此产生的PNP电流增益也较低。这些结构不仅优化了器件响应,适合汽车与工业应用,还可将保护箝位器件的尺寸降至最小,适合不同的目标工作条件。

为了优化保持电压特性,上电ESD与EMI应力条件也必须考虑在内。参考标准规格时,短路时8 kV ESD IEC-61000-4-2应力的双峰值电流波形在第一和第二峰值时分别达到接近30和18.5 A,并且会在500 ns内衰减,而80 V时,85 V EMI ISO- 7637-3脉冲在峰值电流时约为11 A,衰减时间要长得多(约40 μs)。

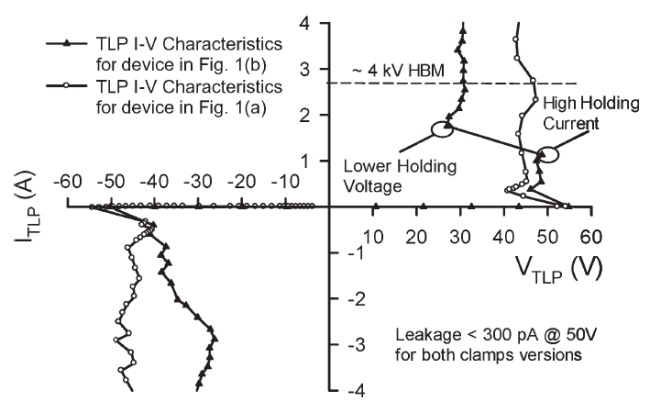

图4,.图1(a)和(b)结构的准静态100 ns TLP双向I–V特性。

图4显示图1中两个器件准静态100 ns TLP I–V特性的对比情况。这些应用中需要考虑的高压内核器件击穿电压通常在100 V范围内,这一数值可作为参考。器件在±40 V以下的正常IC工作时会产生较低的漏电流,从而将能耗及其对电路的影响降至最低。BHEC和BEEC箝位器件均可分别实现高于±40 V和±25 V的最佳目标工作条件,同时保持恶劣工作环境下具有稳定的过应力。注意,BEEC箝位器件除了可提供±25 V以上的保持电压外,还可提供初始高保持电流。这与其使NPN动作更具主导性而产生的应力水平相关。这一特性在箝位器件中很有用,可进一步避免正常工作时的误触发。片内评估能够成功满足电路设计性能和上电ESD和EMI鲁棒性,同时保持较高的FOM比,分别满足BHEC和BEEC箝位器件在FOM ≈ 0.15 mA/μm2和FOM ≈ 0.39 mA/μm2范围内的高保持电压工作[6]。

四、结论

汽车级IC中采用新型三维箝位器件来整合鲁棒性。通过确定互补"T"形与孤岛有效区域,以控制高电平注入再生反馈期间的电子驱动或空穴驱动电流增益,可以最佳状态实现高保持电压双向闭锁箝位。箝位器件已集成至信号调理应用,完全符合汽车级ESD与EMI要求。

- 可靠性工程——关于电子设备静电放电(ESD)防护的设计原则(10-30)

- 静电对家电制造的影响以及设计预防(04-12)

- 深入剖析触控面板的静电放电防护措施(09-21)

- 晶焱科技EMI解决方案(08-23)

- 系统层级静电放电与芯片层级静电放电之差异性(06-03)

- 半导体器件的电气过应力和静电放电故障(10-16)