具有过压保护功能的高端电流检测电路设计

电路功能与优势

发生瞬变后,或者连接、断开或关断监控电路时,高端电流监控器可能遇到过压情况。图1所示电路使用具有过压保护功能、作为差动放大器连接的 ADA4096-2运算放大器来监控高端电流。 ADA4096-2具有输入过压保护功能,对于高于32 V及低于供电轨的电压,不会发生反相或闩锁。

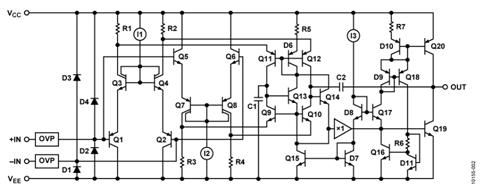

图1. 具有输入过压保护的高端电流检测(原理示意图:未显示所有连接和去耦)

该电路采用可调低压差500 mA线性稳压器 ADP3336供电,如果需要,后者还可用于为系统其他器件供电。设置为5 V输出时,输入电压范围为5.2 V至12 V。为了省电,可通过将 ADP3336 SD 引脚置位低电平来关断电流检测电路,而电源(例如太阳能电池板)仍可工作。这将对未供电的 ADA4096-2的输入端施加电压,但在最高可达32 V的输入电压下不会发生闩锁或损坏。如果需要较低吞吐速率, AD7920 也可在样本间关断。 AD7920在关断时的最大功耗为5 µW,上电时为15 mW。在工作条件下, ADA4096-2仅需120 µA。工作电压为5 V时,功耗仅为0.6 mW。在关断模式下,ADP3336仅消耗1 µA。

图2. ADA4096-2原理示意图

电路描述

该电路是经典的高端电流检测电路拓扑结构,采用单个检测电阻。其他四个电阻(双通道1 kΩ/20 kΩ分压器)处于薄膜网络内(以实现比率匹配),用于设置差动放大器增益。这将放大检测电阻上产生的两个电压间的差异,并抑制共模电压:

VOUT = (VA – VB) (20 kΩ/1 kΩ)

图2显示了 ADA4096-2的原理示意图。输入级包含两个并行的差分对(Q1至Q4和Q5至Q8)。随着输入共模电压接近VCC- 1.5 V,Q1至Q4在I1到达最低顺从电压时关断。相反,随着输入共模电压接近VEE+ 1.5 V,Q5至Q8在I2到达最低顺从电压时关断。此拓扑结构可实现最大输入动态范围,因为放大器在供电轨外的200 mV下(室温)仍可处理输入。

与任何轨到轨输入放大器一样,两个输入对之间的VOS失配决定放大器的CMRR。如果输入共模电压范围保持在各供电轨1.5 V以内,输入对之间的跃迁便可避免,从而将CMRR改进约10 dB。

ADA4096-2输入可保护器件不受最高超出各供电轨32 V的输入电压偏移的影响。此特性对存在电源时序控制问题的应用特别重要,该问题可导致信号源在施加放大器电源之前活动。

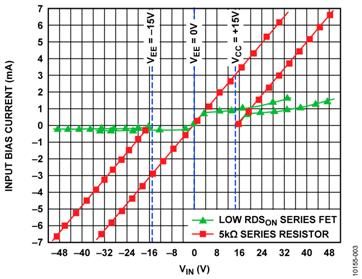

图3显示通过低RDSON内部串联FET(绿色曲线)提供 ADA4096-2的输入电流限制能力,并与使用5 kΩ外部串联电阻和无保护的运算放大器(红色曲线)相比较。

图3. 输入电流限制能力

图3是 ADA4096-2采用单位增益缓冲器配置时的情况,其中将电源连接至GND(或±15 V)并对正输入扫描,直至输入超过电源达32 V。一般而言,输入电流在正过压条件期间限于1 mA,在负欠压条件期间限于200 µA。例如,在20 V过压条件下, ADA4096-2输入电流限于1 mA,从而提供等效于串联20 kΩ电阻的电流限制。图3还显示,无论是否为放大器供电,电流限制电路均有效。

请注意,图3仅代表异常条件下的输入保护。正确的放大器工作输入电压范围(IVR)见 ADA4096-2数据手册的表2至表4。

AD7920是一款12位、高速、低功耗逐次逼近型ADC,采用2.35 V至5.25 V单电源供电,最高吞吐量可达250 kSPS。该器件内置一个低噪声、宽带宽采样保持放大器,可处理13 MHz以上的输入频率。

转换过程和数据采集过程通过CS和串行时钟SCLK进行控制,从而为器件与微处理器或DSP接口创造了条件。输入信号在CS的下降沿进行采样,而转换同时在此处启动。该器件无流水线延迟。

AD7920采用先进的设计技术,可在下述高吞吐速率的情况下实现极低的功耗,若要进入关断模式,必须在SCLK的第2个下降沿之后、第10个下降沿之前的任意时间将CS变为高电平,以中断转换过程。一旦CS在SCLK的此窗口内变为高电平,器件即进入关断模式,CS下降沿所启动的转换终止,SDATA返回三态。如果CS在第2个SCLK下降沿之前变为高电平,则器件仍将处于正常模式,不会关断。这可以避免CS线上的毛刺引起意外关断。

若要退出这种工作模式并使 AD7920再次上电,需要执行一次伪转换。在CS的下降沿,器件开始上电,并且只要CS处于低电平便继续上电,直到第10个SCLK的下降沿之后。经过16个SCLK后,器件完全上电,下一次转换将产生有效数据。

如果CS在第10个SCLK下降沿之前变为高电平,则 AD7920再次返回关断模式。这可以避免CS线上的毛刺引起意外上电,或者CS位于低电平时8个SCLK周期意外爆发。虽然器件可以在CS的下降沿开始上电,但只要不超过第10个SCLK下降沿,便会在CS的上升沿再次关断。

有关时序的详情请参见 AD7920数据手册。

- ADII实验室电路:16位工业、隔离电压电流输出的DAC(02-02)

- ADI实验室电路:低功耗、长距离ISM无线测量节点(02-02)

- ADI实验室电路:16位、100kSPS逐次逼近型ADC系统(02-12)

- ADI实验室电路:如何在IQ调制器的输出端提供固定功率增益(02-21)

- ADI实验室电路:超低功耗数据采集系统(12-14)

- ADI实验室电路:灵活的中频至基带接收机解决方案(12-14)