省电设计将DDS的灵活性扩展到便携式设备

可以是从0?2(C-1)的任意整数。理论上,允许的调谐字范围是从2(C-1)?2C-1,但这会导致奈奎斯特镜像频率(即计数器旋转相量)的合成。根据数字调谐字和DDS采样速率(fS)可以列出熟悉的DDS频率合成方程式,其中,fO为DDS输出频率:

fO/fS=M/2C (1)

因为M必须为整数,所以对于给定的采样速率,传统DDS只能合成2(C-1)个独特的频率。也就是说,当M=0时,输出频率为0(DC);当M=2(C-1)-1时,输出频率只差0.5fS。所有剩余的输出频率都是fs/(2C)(DDS的频率分辨率)的增量。多数情况下,如此精密的频率分辨率是非常令人满意的。例如,AD9913拥有一个32位累加器,其频率分辨率为(250MHz)/232,或者大约0.058Hz。

现在考虑这样一种情况:一个传统DDS具有一个32位累加器,要求利用它来合成一个恰好为采样速率的1/1000的输出频率。这意味着fO/fS=1/1000,将它代入方程式1的左边并求解M可得:M=232/1000,或M=4294967.296。该M显然不是整数,但传统DDS要求M必须是整数值,因此使用它的最接近整数值,本例为4294967。问题在于,使用这个调谐字不能精确地合成0.001fS的频率,而是合成大约0.000999999931fS的频率。在某些应用中,例如网络时钟应用,这一细微的偏差是不可接受的。

传统DDS中的C位相位累加器导致模数(N)是固定的,即N=2C。可编程模数DDS架构对相位累加器进行了巧妙的改造,使得模数可以是满足条件1≤N≤2C的任意整数。也就是说,N值可以由用户设定。对于可编程模数DDS架构,当N=1或N=2时,合成的频率为0Hz,因此可用的最小模数(用于产生DC以外的输出)为N=3。像传统DDS一样,可编程模数DDS也要求方程式1中的M为整数。然而,由于N是可编程的,因此DDS输出频率方程式变为

fO/fS =M/N (2)

方程式2乍看之下平淡无奇,实则颇具意义。考虑选择特定模数N=2C的情况,此时可以合成的频率集与传统DDS相同。然而,可编程模数DDS不仅包括传统DDS的整个频率集,而且包括许许多多的其他频率。这是因为,每个特定的N值(从3到2C)都对应与M(1≤M<0.5N-1)相关的所有频率。对于任何给定的采样速率,它所代表的可能输出频率集远远大于传统DDS。

可编程模数架构的优势在于,几乎所有的有理数频率比都可以合成。例如,现在令M=1、N=1000,就可以精确合成fO=fS/1000的频率。事实上,不仅可以合成fO=fS/1000,还能合成fS/1000的各次谐波(最高499次,即最高谐波次数为0.5N-1)。

在发展可编程模数的同时保持低功耗绝不是小事一桩。看起来很简单,只要增加一些额外的逻辑来改造传统的累加器,迫使它在新模数值时翻滚,但不要忘了,原来的DDS省电创新涉及到角度-旋转算法,它正是基于累加器模数为2的幂这一情况而实现高效运行的。当累加器模数变为2的幂以外的值时,将无法使用省电的角度-旋转算法。

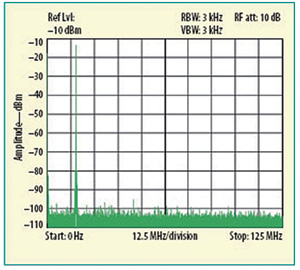

累加器改进的巧妙之处体现在两方面。第一,它一方面允许模数变化,另一方面仍然满足角度-旋转算法的"2的幂"要求。第二,它在实现第一点的同时,将对杂散性能的影响降至最低程度。在图2和图3中,频谱分析仪的扫描频率范围均为0~125MHz,AD9913以250MHz的采样速率工作。图2中,AD9913配置为传统DDS,频率调谐字为262160001(f0≈15.26MHz),这是传统DDS能够实现的最接近M/N=1000/16383的值。图3则使用可编程模数设置。两种情况的频率差仅为大约0.00136Hz(约1MHz)。除了杂散成分略有不同外,两条迹线看起来几乎完全一致。

图2 标准DDS技术的调谐限制

图3 AD9913的可编程模块调谐能力

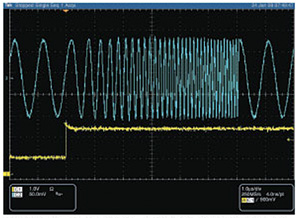

尽管功耗非常低,但AD9913并未减损波形发生能力,仍然能够产生线性频率或相位随时间而以斜坡形式变化的波形。用户设置起点和终点(频率为32位,相位为14位)。两个斜坡方向(从起点到终点和从终点到起点)的步长和步进速率参数都是可以独立编程的。利用这些控制参数和其他用户控制的特性,可以产生多种多样的调制输出信号。图4所示为波形发生能力的一个示例,显示了频率在6μs内从1MHz扫描到10MHz的时域图(6kHz步长、4ns间隔)。下方迹线的上升沿表示频率扫描的起点。到达10MHz后,器件折回并保持1MHz,因此迹线非常清楚地显示了频率扫描的终点。

图4 ADS9913扫频产生的时域波形

AD9913也集成了参考时钟乘法器,支持设计人员使用低频时钟源。除了直接利用高频时钟源来驱动该器件外,设计人员还可以将低频时钟源或晶体谐振器与AD9913集成的PLL(1X至64X)频率乘法器一起使用,产生所需的250 MHz内部采样时钟。采样直接时钟信号时,AD9913的参考时钟(REFCLK)输入端口接受差分或单端信号源。