基于DSP的声雷达信号采集系统

由于系统是包括ADC的数模混合电路,设计中应注意以下问题。在AD7864和CPLD附近大面积的覆铜可以屏蔽外部对模拟信号的干扰,同时AD7864的电源引脚、参考电压输入引脚、VDRIVE引脚与模拟地之间要加0.1μF的贴片电容去耦;数字信号走线和模拟信号走线要分开布放;整板的数字地和模拟地要分开且保证单点相连,相连点选择在了模数信号汇集的地方;为AD7864供电的5V电源需要远离AD7864。

在调试过程中发现,如果不为ADSP-TS201S的JTAG口加驱动芯片,切入硬件仿真环境时Visual DSP会出错,所以建议即使是单片ADSP-TS201系统也要加一片驱动芯片,如TI公司的74ACT11244。

为了提高系统的灵活性,建议为ADSP-TS201S的SCLKRAT0~2(用于选择倍频系数)和DS0~2(用于选择总线驱动能力)引脚分别提供上拉和下拉两种选择,根据调试中的实际情况灵活配置。

3 软件实现

数据采集系统的软件设计部分包括CPLD的软件设计和DSP内部的程序代码。

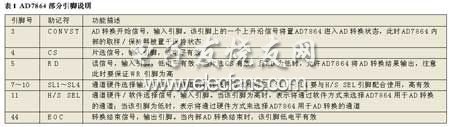

AD7864的一些输入引脚需要进行配置,完成这个任务的是Altera公司的CPLD产品MAX3256A。AD7864需要进行配置的各引脚的具体状态如表1所示。

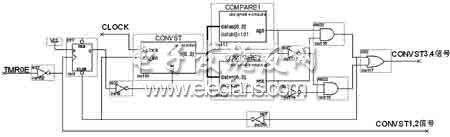

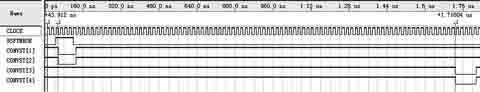

AD7864数据输出控制采取分时输出的方式。4片AD7864分为两组:1、2片一组,3、4片一组。采样信号来自于TS201的定时/计数器,每次定时器计数满时TMROE引脚上会产生4个总线时钟(SCLK,54MHz)的高电平,在CPLD里面把这个信号反向之后作为AD7864的CONVST信号。通过延时3、4片的CONVST信号可以控制两组AD7864分时工作,延时电路及仿真波形如图3所示。通过调节两个比较器的数值,可以产生符合系统需要的波形。

图3 CONVST延时电路及仿真波形

在数据传输上,1、3片的数据占据低位数据线,2、4片的数据占据高位数据线,分时输出防止了总线冲突的出现。由于AD7864-1是补码输出,因此DSP把数据读回后还需作数据提取和符号扩展处理。数据提取主要是把高低位的数据分开,符号扩展是根据采集回来的数据的第12位来判断数据的正负作不同的高位扩展,具体程序如下。

j0 = datum_out0;;

xr0 = [j0+=0];;//读取AD转换的数据

xr1 = 0xfff;;

xr2 = r0 and r1;;//提取AD转换的数据的第12位

xr3 = 0x800;;

xr4 = r2 and r3;;//判断符号位是否为1

if AEQ, jump data(np);;//如果符号位不为1,跳转

xr5 = 0xfffff000;;//如果符号位为1,高位扩展

xr6 = r5 or r2;;

xr2 = xr6;;//xr2里是扩展后的AD转换数据

data:

......//数据进一步处理

结语

经过测试,系统总线在54MHz时钟下正常工作,数据传输正确,在内核时钟432MHz下,圆满完成了数据处理及显示的任务(实际耗时1100M/432M约为2.55s,小于一帧时间)。