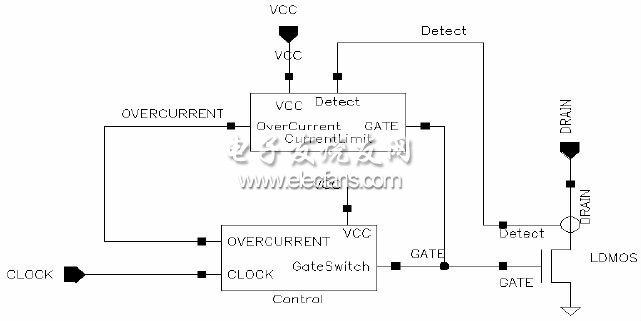

检测LDMOS漏端电压判断是否过流方案

3 仿真结果

我们利用BCD 高压工艺,在cadence 环境下进行电路仿真验证。结果如下:

前沿消隐电路的仿真仿真条件:取电源电压为5.8 V,2 pF 的电容在10μA 的放电电流情况下,延迟时间为Tdelay=C*0.

5VDD/I =2p*2.9/10μ= 0.58μs,仿真结果如图5 所示。

图5 前沿消隐电路仿真

采样电路的仿真

设检测端电压一般在10~50 V 之间变化,我们设置V(Detect)=SIN(30,20,50 k);周期为20μS;又设在采样周期内,比较电压为1 V;依据LDMOS管导通特性,设输出漏电压高于某值(本例为20伏)为过流,则分压比设计为K = R4/ ( R3+R4)=5 k/(5 k+95 k)=1/20, 于是得到采样电压值为V(Sample)=V(Detect)*k =SIN(1.5,1,50 k),即最大值为2.5,最小值为0.5。同样地,我们在采样电路输出端加上一个电容以消除电压尖峰影响。该采样电路仿真结果如图6 所示。

图6 采样电路仿真

比较电压产生器的仿真

在比较电压产生器输出端应加上电容Ccompare,以消除由于开关管导通的瞬间在Ccompare端产生的尖峰电压,仿真结果如图7 所示,其中虚/ 实线分别为有无电容存在时的仿真结果。显然,电容Ccompare的存在极大地改善了输出波形。电容Ccompare大小的选择,应该权衡消峰效果、充电速度和芯片面积消耗间关系。

图7 添加电容Ccompare 前后的比较

本例中,取Ccompare为4 pF。

过流保护电路模块的仿真

对图3 进行电路仿真,电源电压VCC 为5.8 V,LDMOS 漏端检测电压在10~50 V 之间,栅端电压脉冲频率为132 kHz,占空比为60%的方波,SPICE仿真条件设置为VCC=5.8 V,V (Detect)= SIN(30,20,50k),V (Gate)=PULSE(0,5.8,0.5u,0.5u,0.5u,3u,7u),仿真结果如图8 所示。在1.26 uS~4.17 uS 和8.25 uS~11.2 uS 这两个采样区间内,采样电压V(Sample)较比较电压V(Compare)大,输出为低电平(过流保护,低电平有效);在15.2 uS~18.2 uS 采样区间内,采样电压V (Sample) 较比较电压V(Compare)小,输出为高电平,对应不发生过流情况;其他时间段内栅电压处于低电平,对应LDMOS处于关断态,不可能发生过流,故过流输出信号OverCurrent 为高电平。仿真结果表明,该电路确实能很好地实现过流保护的功能。

图8 过流保护电路仿真结果

控制逻辑电路的仿真

在图4 所示的控制逻辑中,设置时钟CLOCK为PULSE (0,5.8,0,0,0,4u,7u), 过流信号OVERCURRENT 在15us 时从高电平跳变为低电平,进行仿真。PULSE 信号记录了CLOCK 信号的开始, 并周期性检测过流信号。当过流信号OVERCURRENT 低电平有效时,R 为高电平,将RS触发器输出Q 复位为低电平,此时FC 为高电平,栅控信号GateSwitch 输出为低电平,关断LDMOS。仿真结果如图9(b)所示。

图9 控制逻辑电路的仿真

闭环控制电路的整体仿真

如图10 所示,图3 电路和外接LDMOS 形成一个闭环控制系统。仿真结果如图11 所示:在没有发生过流时,栅极电压的占空比最大;有过流发生时,过流信号OverCurrent 将栅极电压强制设置为低电平,关断LDMOS,从而达到了过流保护效果。

图10 闭环总体仿真原理图

图11 闭环总体仿真波形

3 结论

本文阐述了几种过流检测方法,分析了每种方法的优缺点。设计了一款闭环控制型的过流保护电路,它采用直接检测LDMOS 管漏端电压的方法,可以克服采用电阻检测时消耗能量,芯片容易发热的缺点,同时提高了开关电源DC/DC 的能量转换效率。另外,采取有比采样电路设计,克服了工艺偏差的影响,提高了采样精度。

基于3μm高压BCD 工艺,我们在Cadence 设计环境中利用电路模拟器Spectre 对该控制电路进行了分模块和整体模块的仿真,结果表明该电路可以较好地实现实时过流保护功能。

LDMOS漏端电压 cadence 电路仿真验证 相关文章:

- 利用Cadence设计COMS低噪声放大器(06-11)

- 中芯国际采用Cadence DFM解决方案(09-21)

- 电源及电源管理方案大联盟(02-05)

- 一种低噪声高增益零中频放大器的设计与实现(05-11)

- 基于Cadence的COMS低噪声放大器设计(02-08)

- Cadence发布业界首款已通过产品流片验证的Xcelium并行仿真平台(02-02)