功率管理优化功率的实现

技术的作用

每一次技术进步的目标都是为了改善性能、密度和功耗。工艺设计者调整施加的电压和氧化物厚度来保持相同电场。该途径在每个新的技术节点都会使功率降低大约50%。但是,随着电压的降低,阈值电压也必须降低,来实现该技术的性能目标。

由于无法立即同时在性能和泄漏方面优化某种技术,因此每种技术通常会有两个变种。一个变种针对高性能,另一个针对低泄漏。二者的首要区别是氧化物厚度、电源电压和阈值电压。栅极氧化物较厚的技术变种面向低泄漏设计,并且必须支持更高的电压来实现合理性能。

方程2表明了依赖于工艺的参数γ和ΘS,你可以操纵它们来控制阈值电压。这些参数取决于杂质浓度,工艺设计者可使用一个额外的注入掩模来调节该浓度。然后你可以运用该方法来控制设计方案的泄漏功率。

在选择技术来优化特定设计的功率时,你必须同时考虑两个方面:需要使用更小的几何结构来降低有功功率;需要使用低泄漏的变种来降低泄漏。但在成本和风险方面需要折中。

更小的几何结构需要在掩模成本和其它一次性工程支出方面投入更多的初始资金。虽然它们凭借每块晶圆可生产出更多器件而具有单位成本优势,但它们也在工艺和设计成熟度方面带来了更高风险。如果设计方案包含SERDES等复杂电路,或是该工艺中新出现的其它敏感的块,那么设计风险可能很高。新技术的工艺缺陷通常是在它投产一年或更久之后被全部消除,然后成品率会稳定下来。

问题的答案取决于功率的性质和最终应用。如果最终应用是由电池供电,那么你必须使泄漏最小化。例如,如果你能关断处于待机模式的设计方案,那么它就不需要低泄漏工艺,这是因为你可以关断高性能系统中的电路,并且同时实现低泄漏的好处。

低泄漏工艺需使用更高的电压,并且一般具有更大的面积,因此对于相同性能,会消耗更大的有功功率。因此对于低泄漏工艺选择工作,泄漏功率是首要推动因素。当泄漏功率在设计方案的工作期间成为总功率的重要部分,或是当设计方案对待机模式的功率(泄漏起着主导作用)有严格要求时,选择低泄漏工艺就能满足这些要求。在其它多数情况下,你可以选择标准工艺,用它和多种电路设计方法来优化功率。

电路设计方法

一旦你选择了某种技术后,你就能专注于设计方法,用它们来优化功率。开始是数字电路中的基本构件:逻辑门。逻辑门一般是标准单元库的零件。标准单元库中的每个门都使用最小的晶体管。每类门都有多个具有不同驱动强度的版本,它们采用更宽的晶体管或多个级来获得更大的驱动电流。由于控制有功功率的主要参数是电源电压,因此单元设计者一般会谨慎设计逻辑门并赋予它们适当的特征,使它们的工作电压比电源电压低30%。该电压具有性能上的含义。降低电源电压可产生更小的电流,导致相同电容的充电和放电时间更长。但是,如果设计方案并未触及特定技术的底线,那么这种减速是可接受的。

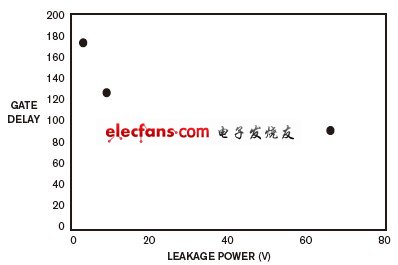

提高阈值电压就能降低器件中的泄漏电流。你可以用包括标准、高、低阈值电压器件在内的多阈值电压器件来设计逻辑门,由此控制泄漏功率。目前,用多电压阈值器件来设计标准单元库是常见做法。对于你用标准、高和低阈值电压器件实现的与非门,在泄漏和性能之间存在折中(图3)。

图3,泄漏和功率之间存在折中。

下一个因素是沟道长度。单元设计者用最小沟道长度的器件创造标准单元库中的逻辑门。通过增加沟道长度,你可以降低器件中的泄漏电流,但这么做也会降低晶体管的导通电流并使它减速,标准单元库提供商最近创造了一些具有多种沟道长度的标准单元。多阈值电压器件和多种沟道长度共同提供了一个丰富的功率管理标准单元库。

另一种方法是反向偏压。传统上,数字技术设计者把MOS晶体管看作是三端子器件,其中的基底连接到源极。结果,反向偏压始终为0 V。通过把基底作为单独的端子,并施加反向偏压,你可以提高阈值电压并降低泄漏。你可把N沟道器件基底连接到很高的负电压,并把P沟道器件基底连接到很高的正电压。你需要很大的电压来实现阈值的小变化,这是因为反向偏压与阈值电压是平方根关系,并且存在体偏压系数γ。

相同方法还适用于存储器设计。存储器在其位单元和外围电路中都可能有高阈值电压器件,并具有反向偏压控制来管理关断状态时的泄漏。把不同的阈值电压器件组合用于位单元和外围电路,这可提供广泛的存储器泄漏控制和多个性能级别。如果降低存储器的电源电压,就会使性能明显下降。

功率管理

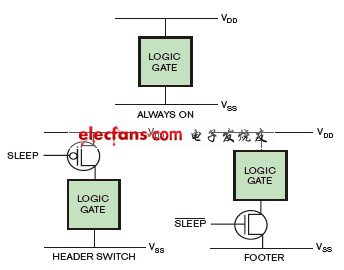

在研究了电路级的功率管理方法后,你可以研究芯片级的方法。第一种是当电路不工作时,用电源开关来关闭它们。在关闭模式中,电路仅消耗泄漏功率,不消耗有功功率。你可把MOSFET用作连接到电源轨和接地轨的开关,来关闭电源(图4)。在实现关闭时,你必须考虑电路如何苏醒,并且有时你必须保持设计方案的状态。在此情形中,你可使用保持双稳态多谐振 荡器来存储状态。

图4,可以用头开关和脚开关来关断逻辑电路,以便节省有功功率。

在控制设计方案的哪些零件需要关闭方面,你可以用电源开关来提供多级粒度。你可以在逻辑门级开关电源,为每个门配备连接到电源的头开关(header switch)和脚开关(footer switch)。或者你可以把头开关和脚开关与逻辑集群一起使用,或是在块级与功率岛一起使用。你还可以简单地把功率岛连接到不同的电源,设计方案在外部接通或关断电源,由此在不使用电源开关的情况下使用功率岛。

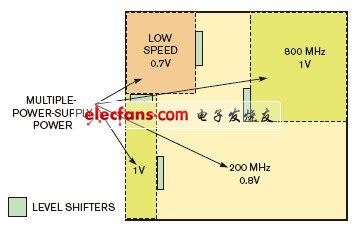

多电源设计方案配备具有不同值的功率岛(图5)。该方法使较慢的逻辑块能以较低电压运行,由此省电。对于多电源设计方案,你必须在功率岛边界插入电平移位单元。这些单元把逻辑电平转换成它们连接的功率岛的恰当电平。统一功率格式(UPF)语言使芯片设计者能描述带有电源选通和多个电源的设计方案。它允许定义隔离单元、电平移位器、电源选通开关。共同功率格式(CPF)是一种相似的语言,具有相同目的。这些语言目前在彼此竞争,以便成为定义设计方案功率管理的唯一标准。

图5,在具有多个电源域的芯片中,低性能部分使用功率较低的电源来降低功率。电平移位器恰当地连接了不同域中的逻辑电路。

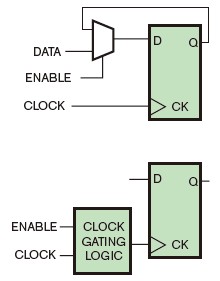

目前的EDA工具有效地支持这些功率管理方法。它们还在实现期间提供额外的省电效果。由于时钟网络和它们驱动的双稳态多谐振荡器消耗大量电力,因此你可以在不需要它们运行时关断时钟(即选通时钟),由此实现省电。时钟选通可在双稳态多谐振荡器的输入端不工作的周期内,取消该振荡器中的时钟活动(图6)。

图6,时钟选通在双稳态多谐振荡器的输入端不工作的周期内取消该振荡器中的时钟活动。

你还能优化时钟分配网络中的功率。利用克隆方法,你可以把时钟树分解成更小的部分,由此降低时钟网络的总电容和功率。物理优化过程也考虑了功率。一旦你满足了时序约束,物理优化就会减少非关键路径中的门,来降低功率,并且不影响时序。

- 优化移动多媒体传输链的功耗(05-25)

- 功率管理技术介绍(09-26)

- 讨论DSP系统中延迟电池寿命关键--DC/DC稳压器(03-11)

- 危害锂电池寿命的几大“误区”(07-29)

- 利用超级电容延长交通运输和移动应用中的电池寿命(02-10)

- TI分享五大妙招,轻松应对电源挑战(06-22)