谈DC-DC效率:提高能效的新方法

功率半导体获得如此多的关注实属罕见,但即使是小小的半导体也能够在能效方面做出巨大的贡献。当前的"绿色"系统趋势不仅意味着采用环保元件,还为电子产业带来了艰巨的挑战:即节能和提高系统级效率。基于此,功率硅产品如功率MOSFET 正在市场上炙手可热,因为对任何低压转换而言,绝大部分在线损耗都是由这些器件产生的,而这直接关系到系统的总体效率。

由于业界的巨大努力与关注,计算和消费电子产品在提高功效和降低功耗上已取得惊人的进步。一直以来,业界焦点都放在 AC-DC "银盒子"转换上面。然而,随着80 PLUS、Climate Savers 和能源之星 (EnergyStar 5) 等法规的出台,设计人员开始认识到 AC-DC 和 DC-DC 功率系统都需要进一步改进。AC-DC 系统的平均效率一般在 65% 左右,而 DC-DC 系统则为 80%,因此前者的改进空间较大,对其更为关注也是不难理解的。目前正是重新审视 DC-DC 系统,寻找能提升效率的创新方法的时候了。

在计算、通信和消费应用系统中,DC-DC 系统负责转换、管理和分配能量,为图形卡、处理器芯片和内存等器件供电。随着对更高性能和功能性的需求不断增加,这些器件的耗电量比以往更甚。计算和消费电子产品的设计人员不得不在功率预算和效率、成本及性能之间进行权衡。为此,人们一直在就如何评估开关电路以及其所采用的功率晶体管器件展开研究,同时也在 MOSFET 器件和先进的热封装技术方面取得进展。EnergyStar 和 80 PLUS 法规的出台对各种消费电子产品,尤其是计算产品意味着有了规范要求。延长电池寿命也是当今便携设备用户的一个呼声。因此,延长电池寿命、减小波形因数,以及新的政府法令要求,都在促使设计人员仔细选择电源部件,尤其是板上同步降压转换器。这使新平台在功率密度、效率和热性能上有了显著的改进。例如,已有 50 万台服务器完全达到 80 PLUS 能效要求,一年节省的能量足以供应 377,000 多户欧洲家庭所需。

电路和损耗

同步降压电路是低压DC-DC功率管理系统的主要部分,而导致DC-DC同步降压电路效率降低的主要因素在于MOSFET的开关损耗和传导损耗。

图1所示为桌面计算机典型的单相降压调节 (VRM)。在满载时一般将产生高达25A的电流,并可在12V输入下,以1.2V输出电平输出这样的电流。为此,主通道电路上 (或者说高位) 就得有一个MOSFET;而在同步侧 (或者说低位) 就有两个并联的MOSFET。从12V降到1.2V意味着有10% 的占空比,只有这样,高位MOSFET才会实现低开关损耗,而低位的一对MOSFET才会有最低的导通电阻RDS(ON),从而最大限度地降低传导损耗。

图1 台式电脑典型的单相VRM

在采用分立元件驱动电路和MOSFET的多相位VRM解决方案中,典型的峰值效率在每相额定电流为10A时一般为90%,而当电流为满负载30A时效率降到85%。这10%~15% 的系统能效损耗直接正比于功率和热耗散。直接来说,所有功率系统设计人员都在努力使损耗和热耗散达到最小。就当今的设计而言,VRM系统一般输出功率在100W,运行效率为85%,这就是说,所有的桌面计算机都浪费了15% 的功率。

MOSFET硅技术的演进

MOSFET厂商一直主要在两个方面优化其半导体开发。首先是改进新产品的开关特性 (开关速度),采用先进的栅极结构,从而减弱器件的栅极电荷 (Qg) 效应。其次是提高单元密度,即在晶片尺寸不变的前提下,状态电阻 (R) 显著降低。按功率的数学定义,导通RDS(ON) 和电流是决定MOSFET传导损耗的两个因素。

从上面的公式可看出,如果改进MOSFET器件,降低导通电阻RDS(ON和缩短开关跃迁时间TRISE 和TFALL,就能减少功率损耗 (PLOSS)。

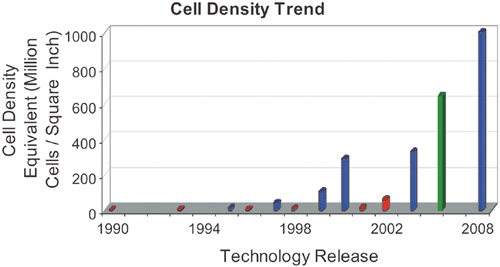

图2所示为飞兆半导体30V以下N沟道MOSFET器件在单元密度上的改进情况。图中,每个柱条代表一次新的工艺变革。从此图可看出,在最近10年,单元密度已经从每平方英寸3200万发展为当今的每平方英寸10亿。

图2 单元密度的演进

[图中文字:单元密度的发展趋势;技术发布,单元密度数值(百万单元数量/平方英寸)

在业界,有一个普适的性能测量始终是基准,即品质因数 (FOM),而且基本上是半导体硅片导通电阻 (RDS(ON)) 和栅极电荷 (Qg) 的总和。

FOM = RDS(ON) x QG

如前所述,RDS(ON) 直接关系到传导损耗,QG直接关系到开关损耗,因此,FOM越低,器件性能就越好。

图3所示为飞兆半导体的低压MOSFET工艺技术的演进。2004年推出的PowerTrench 3代,最佳FOM为240,而今天的PowerTrench 5代,最佳FOM为126。

不幸的是,FOM降低50%,并不能使MOSFET的损耗也降低50%,因为两者并非线性关系。不过,只要仔细选择器

- 同步降压转换器电路设计基础(01-01)

- 电源设计小贴士 39:同步整流带来的不仅仅是高效率(10-25)

- 同步降压转换器的布局注意事项(11-22)

- 新型灌封式6A至12A DC-DC μModule稳压器系列(11-19)

- DC-DC开关变换器中混沌现象的研究综述(11-27)

- 数码相机电源电路设计及DC/DC变换器选择(01-22)