新型BiCMOS集成运算放大器设计

为了提高运算放大器的驱动能力,依据现有CMOS集成电路生产线,介绍一款新型BiCMOS集成运算放大电路设计,探讨BiCMOS工艺的特点。在S-Edit中进行"BiCMOS运放设计"电路设计,并对其电路各个器件参数进行调整,包括MOS器件的宽长比和电容电阻的值。完成电路设计后,在T-spice中进行电路的瞬态仿真,插入CMOS,PNP和NPN的工艺库,对电路所需的电源电压和输入信号幅度和频率进行设定调整,最终在W-Edit输出波形图。在MCNC 0.5μm工艺平台上完成由MOS、双极型晶体管和电容构成的运算放大器版图设计。根据设计的版图,设计出Bi-CMOS相应的工艺流程,并提取各光刻工艺的掩模版。

1 电路图设计

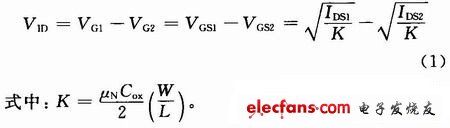

本文基于MCNC 0.5 μm CMOS工艺线设计了BiCMOS器件,其集成运算放大器由输入级、中间级、输出级和偏置电路4部分组成。输入级由CMOS差分输入对即两个PMOS和NMOS组成;中间级为CMOS共源放大器;输出级为甲乙类互补输出。图1为CMOS差分输入级,可作为集成运算放大器的输入级。NMOS管M1和M2作为差分对输入管,它的负载是由NMOS管M3和M4组成的镜像电流源;M5管用来为差分放大器提供工作电流。M1管和M2管完全对称,其工作电流IDS1和IDS2由电流源Io提供。输出电流IDS1和IDS2的大小取决于输入电压的差值VG1-VG2。IDS1和IDS2之和恒等于工作电流源Io。假设M1和M2管都工作在饱和区,那么如果M1和M2管都制作在孤立的P阱里,就没有衬偏效应,此时VTN1=VTN2=VT。忽略MOS管沟道长度的调制效应,差分对管的输入差值电压VID可表示为:

M2管和M4管构成CMOS放大器,两个管子都工作在饱和区,其电压增益等于M2管的跨导gM2和M2,M4两管的输出阻抗并联的乘积,即:

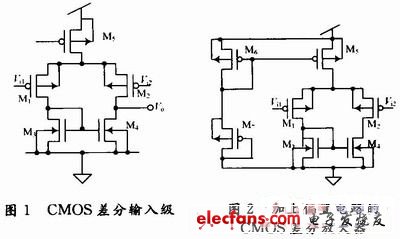

式(4)表明,CMOS差分放大器具有较高的增益。该增益随电流的减少而增大;随MOS管宽长比的增加而增高;随两只管子沟长高调制系数λ的减少而增加,所以设计时,应尽可能增加沟道长度,减小λ值,以此来提高CMOS的增益。偏置电路用来提供各级直流偏置电流,它由各种电流源电路组成。图2为加上偏置电路的CMOS差分放大器。

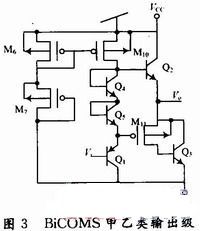

图2中,M5管为恒流源,用于为差分放大器提供工作电流;M6和M7管为恒流源偏置电路,用于为M5提供工作电流。其中,基准电流为;

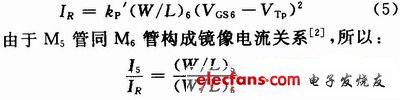

图3为输出级的最终结果,其中M6,M7,M10为偏置,Q4,Q5用来减小交越失真,Q1为输出级的缓冲级。

2 电路仿真

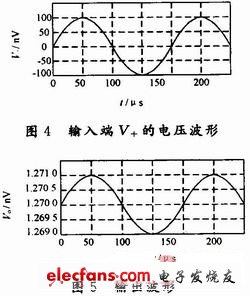

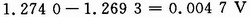

Aod是在标称电源电压和规定负载下,运算放大器工作在线性区,低频无外部反馈时的电压增益,Aod的值越大越好。图4为输入端V+的电压波形。由图可见V+的峰峰值为200 nV,输入端V-的电压为0。图5为输出波形(在Q3的集电极输出)。

由图5可见,输出电压的峰峰值为:

因此开环差模电压增益为:

可以测量出共模电压增益,满足设计要求。

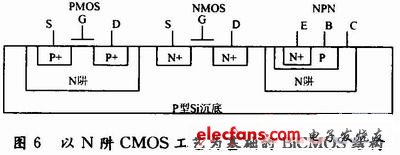

3 版图设计

采用的是以CMOS工艺为基础的BiCMOS兼容工艺。首先以外延双阱CMOS工艺为基础,在N阱内增加了N+埋层和集电极接触深N+注入,用以减少BJT器件的集电极串联电阻阻值,以及降低饱和管压降;其次用P+区(或N+区)注入,制作基区;再者发射区采取多晶硅掺杂形式,并与MOS器件的栅区掺杂形式一致,制作多晶硅BJT器件。由此可见,这种高速BiCMOS制造工艺原则上不需要增加其他的重要工序。

由于基准电路不易调整,在设计版图时将基准部分外接。基于0.5μm CMOS工艺的运算放大器版图如图7所示。

4 结语

该运算放大器结合了CMOS工艺低功耗、高集成度和高抗干扰能力的优点,双极型器件的高跨导,负载电容对其速度的影响不灵敏,从而具有驱动能力强的优点。该BiCMOS器件在现有CMOS工艺平台上制造。该放大器以CMOS器件为主要单元电路,在驱动大电容负载之处加入双极器件的运算放大器电路,然后在Tanner Por软件平台上完成电路图的绘制、仿真,并在MCNC 0.5μm CMOS工艺线上完成该电路的版图设计,经实用,运算放大器的参数均达到了设计要求。

- 运算放大器的选择(03-18)

- 运算放大器的输入级(03-18)

- 运算放大器电路固有噪声的分析与测量(第二部分):运算放大器噪声介绍(05-12)

- 运算放大器电路固有噪声的分析与测量(第二部分):运算放大器噪声介绍(二)(05-12)

- 运算放大器电路的固有噪声分析与测量(07-14)

- 揭示运算放大器未来发展趋势,创新技术带来电子设计新变革(11-27)