数字信号处理器(DSP)在串联型电力有源滤波器中的应用

1引言

应用电力电子技术抑制谐波,以改善电能质量的新技术——电力有源滤波器(ActivePowerFilter)已成为近年来电力系统研究领域中新的热点。国际上以抑制谐波电流为目的的并联型电力有源滤波器应用居多,而随着电压敏感性负载不断增多,以电压畸变治理为主的串联型有源滤波器,正显示着越来越大的利用价值。同时,它又是进一步研究综合电能质量补偿器的前提条件,因此,对串联型有源滤波器进行研究有着重大的意义。

在串联型有源滤波器的研制过程中,我们采用了美国德州仪器公司(TI)的TMS320F240数字信号处理器(DigitalSignalProcessor),极大地方便了软硬件的开发,加快了研制的进程。

TMS320F240具有下述特点【2】【3】:

(1)50ns的指令周期,在一个指令周期内可完成

一次乘法和一次加法;

(2)大容量的片内存储器:包含544字×16位的

片内数据/程序双口(DualAccess)RAM,16k字×16位的片内FlashEEPRO,共计224k字×16位存储器地址范围(64k数据,64k程序和I/O以及32k全局存储器空间);

(3)事件管理模块:12路比较/脉冲宽度调制(PWM)通道,3个16位通用定时器,3个死区控制的16位全比较单元,4个捕获单元;

(4)双10位A/D转换模块;

(5)基于锁相环(PLL)的时钟模块;

(6)看门狗定时器模块(具有实时中断功能);

(7)6个外部中断(电源驱动保护、复位、NMI及3种可屏蔽中断)。

充分使用TMS320F240DSP芯片构成的实用系统,具有扩充的外围电路少、控制电路简单、控制手段灵活、易调试和易维护等很多特点。

2以DSP为核心的硬件结构

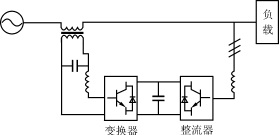

串联型电力有源滤波器主电路由串联电路和并联电路组成,结构如图1所示。

图1串联型电力有源滤波器主电路

串联电路功能是:检测电网畸变电压,分离出需要补偿的电压并产生控制信号,生成补偿电压注入电网,实现电压补偿的功能。并联电路功能是:检测有源滤波器输入电流,生成电流控制信号,从而维持电容电压恒定和保证设备功率因数。同时,作为一个实用装置,还必须实现相应的投入、切除手段和故障情况下的保护手段。

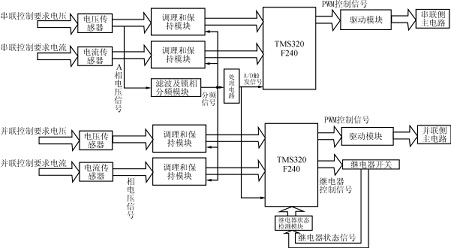

控制电路以DSP为核心,其结构框图如图2所示。

图2以DSP为核心的控制结构框图

电网电压、电流经过传感器后变成+5V~-5V的弱电信号,经过调理电路后变成0~5V的信号,其中从电压互感器来的A相电压信号经带通滤波后送入锁相分频模块,产生采样保持分频窄脉冲信号来控制保持电路,使之每个工频周期保持指定点。而分频窄脉冲经过处理电路的处理后作为DSP内部A/D的起动信号使用。

主电路的控制采用两片TMS320F240。一片作为主DSP,除负责并联整流控制(产生并联侧整流及输入电流控制PWM信号驱动并联侧主电路)外,还承担整套装置的协调工作,包括投入切除算法控制,故障保护控制及故障检测功能。它的输出信号一部分用于控制驱动模块以得到恒定的直流电容电压,另一部分控制主电路继电器。而另一片作为从DSP,用于串联侧的电压补偿PWM控制信号的产生,TMS320F240将电压电流采样信号经过DSP检测算法运算后生成补偿信号,补偿信号通过TMS320F240内部PWM控制模块产生PWM控制信号送给驱动模块,经由驱动模块驱动主电路生成补偿电压注入电网。

3DSP软件的设计

DSP完成了APF系统中的绝大多数功能,为了完成这些功能,除用到TMS320F240的核心部分外,还充分应用了F240片内的许多外围模块,如A/D模块,事件处理模块和外部中断功能。整个算法由并联侧与串联侧算法构成。

3.1并联侧DSP软件算法

(1)整体软件流程

并联侧DSP除完成并联整流算法外,还需要完成APF设备的投入和切除算法,故障检测和故障控制算法。图3是并联侧DSP软件算法的流程图。

图3并联侧DSP软件算法的流程图

如图3所示,当DSP起动后首先进行设备初始化操作,结束后进行设备投入电网操作,然后DSP空闲,等待中断的发生,一旦中断出现,运行相应的中断处理程序,处理完成后DSP空闲等待另一个中断的发生。A/D变换,控制算法和PWM产生等一系列过程都在外部中断XINT3中断服务程序中完成。

在设备初始化过程中,完成对故障检测中断设置、DSP的PLL锁相时钟模块设置,外部

数字信号处理器(DSP) 电力 有源滤波器 相关文章:

- 电力电缆布线热伸缩及其对策浅谈(07-28)

- 电力电缆故障测量中接地电流消除方法的研究(11-24)

- 打开通往未来智能电网之路(02-28)

- 基于DSP单周控制有源电力滤波器的研究(06-01)

- 高频开关电源的特点及在电力系统的应用(06-09)

- 电力机车辅助电源系统的分析与比较(10-28)