一种基于PWM的CMOS误差放大器的设计

3 误差放大器仿真结果

在Cadence软件中搭建模拟仿真验证平台,在电源和地线之间接入5 V直流电压,误差放大器的正向输入端接入1.12 V的直流电压(这个电压取值在系统中由带隙基准电压源产生),反向输入端输入一个直流电位为1.12 V的正弦波。由于放大器的电压增益较大,如果正弦波的交流幅度较大,会使得输出出现失真,因此,这里将反相输入端的正弦波电压选取1 mV的交流幅度输入。

首先要进行直流工作点的验证。通过dc仿真,观测电路中的MOS管工作状态,如果有不在饱和区的管子,需要根据调整MOS管宽长比,直至所有管子的工作区(region)都显示为"2"。

直接测试电源电压端的电流值,即可得到误差放大器的静态总电流。测得这个电流值I为173.4μA,由此可计算出误差放大器的静态总功耗:

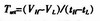

进行瞬态仿真,仿真结果如图3所示。观察电路波形,确认模块实现了电压的比较和误差的放大功能。由瞬态仿真波形图可以看出,输入差模电压为1 mV时,输出电压最大值可达4.15 V,最小值接近1.52 V,输出摆幅不小于2.63 V。加大信号,可测得输出电压的建立时间:

计算可得上升建立时间和下降建立时间分别为6.7 V/μs和5.7 V/μs。

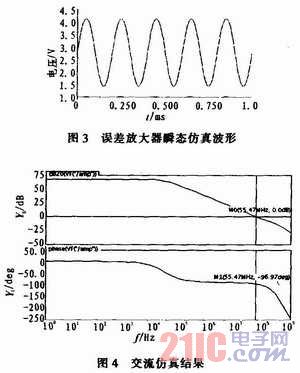

对电路进行交流增益仿真,观察电路增益和单位增益带宽,结果如图4所示。

根据交流仿真结果可知,电路0 dB带宽达到55.5 MHz,电压开环增益约67.2 dB,相位裕度为180°-96.97°≈83.0°。

共模抑制比CMRR是放大器对输入端共模信号的抑制能力,其计算表达式为

其中Avd表示差模增益,Avc表示共模增益。把运算放大器连接成单位增益负反馈的模式,在运算放大器的同相和反相输入端加上相同的交流电压,进行交流仿真,得到的仿真结果如图5所示,该曲线是1/CMRR,因此可以得到运算放大器的低频共模抑制比为49.17 dB。

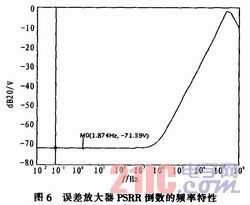

电源抑制比PSRR是衡量电路对电源噪声的抑制能力,把运算放大器连接成单位增益负反馈的模式,仅在供电电压源上增加1 V的交流电压,测试结果如图6所示,该曲线是1/PMRR,因此运算放大器的低频电源抑制比为71.39 dB,各项指标达到预期要求。

4 结论

为解决PWM控制器中输出电压与基准电压的误差放大问题,本文设计了一款高增益,宽带宽,输出摆幅可以控制的新型误差放大器。通过在二级放大电路中间增加一级缓冲电路,克服补偿电容的前馈效应,同时消除补偿电容引入的零点。通过交流仿真验证,电路0 dB带宽达到55.5 MHz,电压开环增益约67.2 dB,相位裕度为83.0°上升建立时间和下降建立时间分别为6.7 V/μs和5.7 V/μs,共模抑制比和电源抑制比分别为49.17 dB和71.39 dB。其突出优点是自顶向下设计,每一个器件的具体参数先通过手工计算再用软件仿真逐步调整获得,查找和修改错误方便,具有较大的灵活性。该误差放大器已经成功运用到PWM芯片中,其独特的结构使得PWM的最大输出占空比和最小输出占空比可以控制,大幅提升了芯片系统的整体性能。

- 0.5μm CMOS带隙基准电路设计(01-13)

- 一个高性能带隙基准电压源的设计(06-09)

- 一种快速响应LDO环路设计(06-28)

- ADC输入转换器电路分析 (02-14)

- 如何选择基准电压源?(02-18)

- 产生稳定电压的基准电压元件(07-14)