高速ADC模拟电源的详细设计方案

束条件。

请记住,使用LC配置测试PSRR/PSMR时有一个缺点。当扫描目标频段时,为使ADC电源引脚达到所需的输入电平,波形发生器输出端所需的信号电平可能非常高。这是因为LC配置会在某一频率(该频率取决于所选的值)形成陷波滤波器。这会大大增加陷波滤波器处的接地电流,该电流可能会进入模拟输入端。要解决这一问题,只需在测试频率造成测量困难时换入新的LC值。这里还应注意,LC网络在直流条件下也会发生损耗。记住要在ADC的电源引脚上测量直流电源,以便补偿该损耗。例如,+5V电源经过LC网络后,系统板上可能只有+4.8V。要补偿该损耗,只需升高电源电压即可。

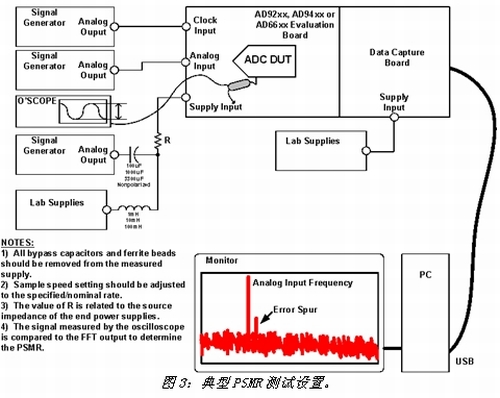

PSMR的测量方式基本上与PSRR相同。不过在测量PSMR时,需将一个模拟输入频率施加于测试设置,如图3所示。

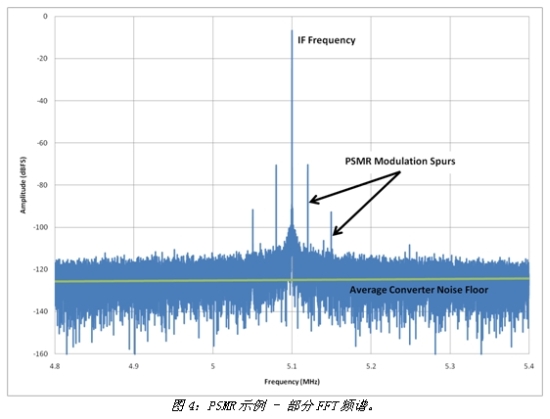

另一个区别是仅在低频施加调制或误差信号,目的是观察此信号与施加于转换器的模拟输入频率的混频效应。对于这种测试,通常使用1-100kHz 频率。只要能在基频周围看到误差信号即混频结果,则说明误差信号的幅度可以保持相对恒定。但也不妨改变所施加的调制误差信号幅度,以便进行检查,确保此值恒定。为了获得最终结果,最高(最差)调制杂散相对于基频的幅度之差将决定PSMR规格。图4所示为实测PSMR FFT频谱的示例。

电源噪声分析

对于转换器和最终的系统而言,必须确保任意给定输入上的噪声不会影响性能。前面已经介绍了PSRR、PSMR及其重要意义,下面将通过一个示例说明如何应用所测得的数值。该示例将有助于设计人员明白,为了了解电源噪声并满足系统设计需求,应当注意哪些方面以及如何正确设计。

首先选择转换器,然后选择调节器、LDO、开关调节器或其它器件。并非所有调节器都适用。应当查看调节器数据手册中的噪声和纹波指标,以及开关频率(如果使用开关调节器)。典型调节器在100 kHz带宽内可能具有10 μV rms噪声。假设该噪声为白噪声,则它在目标频段内相当于31.6 nVrms/rt-Hz的噪声密度。

接着检查转换器的电源抑制指标,了解转换器的性能何时会因为电源噪声而下降。在fs/2的第一奈奎斯特区,大多数高速转换器的PSRR典型值为 60 dB (1 mV/V)。如果数据手册未给出该值,请按照上述方法进行测量,或者询问厂家。

使用一个2Vpp满量程输入范围、78dB SNR和125MSPS采样速率的16位ADC,其噪声基底为11.26 nVrms。任何来源的噪声都必须低于此值,以防其影响转换器。在第一奈奎斯特区,转换器噪声将是89.02 μV rms (11.26 nVrms/rt-Hz) × sqrt(125MHz/2)。虽然调节器的噪声(31.6 nv/rt-Hz)是转换器的两倍以上,但转换器有60dB的PSRR,它会将开关调节器的噪声抑制到31.6 pV/rt-Hz (31.6 nV/rt-Hz × 1 mV/V)。这一噪声比转换器的噪声基底小得多,因此调节器的噪声不会降低转换器的性能。

电源滤波、接地和布局同样重要。在ADC电源引脚上增加0.1μF电容可使噪声低于上述计算值。请记住,某些电源引脚吸取的电流较多,或者比其它电源引脚更敏感。因此应当慎用去耦电容,但要注意某些电源引脚可能需要额外的去耦电容。在电源输出端增加一个简单的LC滤波器也有助于降低噪声。不过,当使用开关调节器时,级联滤波器能将噪声抑制到更低水平。需要记住的是,每增加一级增益就会每10倍频程增加大约20dB。

最后需要注意的一点是,上述分析仅针对单个转换器而言。如果系统涉及到多个转换器或通道,噪声分析将有所不同。例如,超声系统采用许多ADC通道,这些通道以数字方式求和来提高动态范围。基本原理是:通道数量每增加一倍,转换器/系统的噪声基底就会降低3dB。对于上例,如果使用两个转换器,转换器的噪声基底将变为一半(-3dB);如果使用四个转换器,噪声基底将变为-6dB。之所以如此,是因为每个转换器可以当作不相关的噪声源来对待。不相关噪声源彼此之间是独立的,因此可以进行RSS(平方和的平方根)计算。最终,随着通道数量增加,系统的噪声基底降低,系统将变得更敏感,对电源的设计约束条件也更严格。

本文小结

要想消除应

- 12位串行A/D转换器MAX187的应用(10-06)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 12位串行A/D转换器的原理及应用开发(10-09)

- 在射击探测器中增加口径确定功能的简单电路(11-13)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 深入解析:模拟前端模/数转换器的三种类型 (11-26)