GPS接收机载波跟踪环路设计

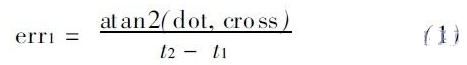

I 和Q 的采样时间不应跨越数据比特的跳变,在初始信号捕获期间,接收机并不知道数据跳变的边界在哪里。在完成比特同步的同时,与相位锁定相比,一般说来更易与卫星信号保持频率锁定。常用的频率鉴别器为四象限反正切鉴别器,其表达式为:

式中: cr ss = I ps1×Qps2 - I ps2 Qps1 ;dot = I ps1×I ps2 + Qps1×Qps2 ;I ps1 和Qps1 是在时刻t 1 下的相关值;I ps2 和Qps2 是在时刻t2 下的相关值;t2- t1 为预检测积分时间。

采用这种鉴别器,t1 和t2 时刻的相关值采样应该在同一数据比特时间区间内,但是初始捕获阶段接收机不知道数据跳变的边界,所以本文采用二象限反正切鉴别器,有效防止了因数据跳变引起的频率鉴别误差,其表达式为:

3 相位鉴别器

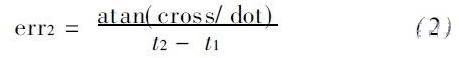

PLL 通过复现卫星的准确相位和频率( 已变换到中频) 来完成载波剥离功能。因为CoSTas 锁相环对数据调制不敏感,所以本文采用Costas 锁相环,常用的鉴别器如表1 所示。

表1 常用Costas 环鉴别器

因为二象限反正切鉴别器的输入误差范围在±90°区间上保持线性,所以本文采用二象限反正切鉴别器。

4 载波环滤波器

环路滤波器的作用是降低噪声,以便对原始信号进行精确估计,其阶数和带宽决定了它对信号的动态响应。为了使接收机适应高动态环境,本文采用二阶FLL 辅助三阶PLL 的环路滤波器,其原理框图见图2。

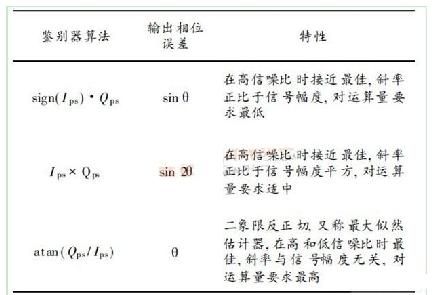

环路滤波器的特性见表2。

接收机完成捕获、码跟踪后进入载波跟踪模块,由于此时多普勒频移较大,所以FLL 与PLL 同时工作,给环路滤波器输入频差和相差,当频率误差减小到PLL 可以容忍的范围时,将环路滤波器的输入频差设为零,即环路转变为纯PLL 跟踪模式。

表2 环路滤波器特性

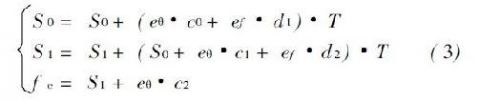

由图2,环路滤波器的表达式为:

根据接收机的使用环境,确定环路滤波器的噪声带宽 Bnf 和B np ,就可以由表2 确定滤波器系数。注意,FLL 向滤波器的系数插入点与PLL 相比要提前一个积分器,这是因为FLL 误差的单位是Hz,而PLL 误差的单位是相位单位。

图2 二阶FLL 辅助三阶PLL 滤波器

5 仿真结果及分析

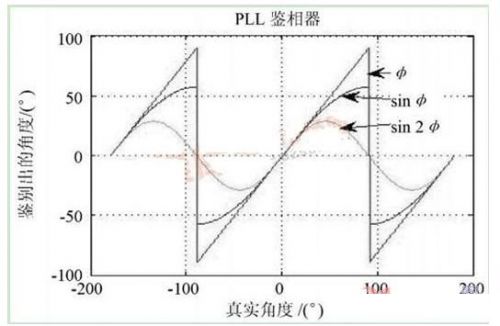

5. 1 FLL 鉴别器特性

采用预检测积分时间T= 1 ms,在有数据调制的情况下( ±1 跳变/ ms) ,输入频率误差范围为± 400 Hz,对四象限反正切( atan2) 和二象限反正切( atan) 鉴别器进行仿真,结果见图3。由图3 可以看出,atan2 鉴别算法已不能鉴别出真正的频率误差,而atan 可以鉴别的范围达到±250 H z。

图3 有数据调制下的FLL 鉴频特性

5. 2 PLL 鉴别器特性

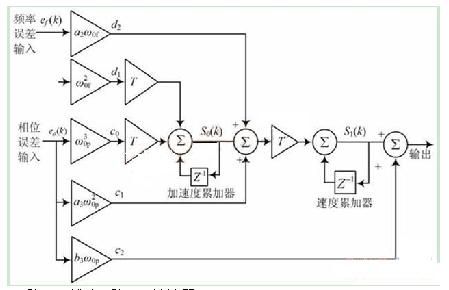

采用预检测积分时间T= 1 ms,输入相位误差范围为±180°,对表1 的三种相位鉴别器进行仿真,结果见图4。通过图4 可看出,只有二象限反正切( atan) 鉴别器在±90°的范围内保持线性,且斜率与信号幅度无关。

图4 PLL 鉴相特性

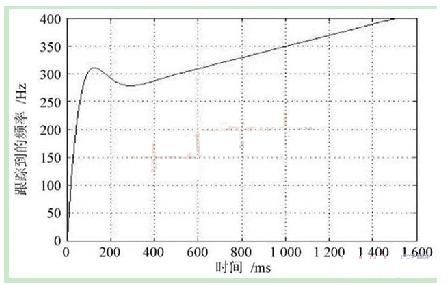

5. 3 载波跟踪环仿真及分析

根据5. 1 和5. 2 节的仿真结果,FLL 选择二象限反正切鉴别器,PLL 也选择二象限反正切鉴别器。将鉴别器结果送入图2 所示的环路滤波器,滤波结果送给数控振荡器,形成图1 所示的闭环模式。接收机捕获时采用时域和频域二维搜索算法,根据FLL 鉴别器的频率鉴别范围,设定频率搜索步长为500 Hz。接收机速度为500 m/ s,加速度为10g 时的仿真结果如图5 所示。由图5 可以看出,载波跟踪环路可以快速、准确地跟踪频率的变化,在3~ 4 s 即可达到锁定状态。

图5 跟踪到的频率变化曲线

6 结 语

采用了二阶锁频环辅助三阶锁相环的载波跟踪环路。通过仿真可以看出,选用的鉴别器鉴别范围大,精度高,且对数据跳变不敏感。由鉴别器、环路滤波器和数控振荡器形成闭环回路,在高动态环境下,环路锁定时间短,载波测量精度高,具有一定的实用价值。

- D类音频功率放大器的环路设计(11-20)

- 车载GPS智能终端的设计与实现(03-04)

- 智能型手机电源管理系统的设计(05-05)

- GPS高精度的时钟的设计和实现(10-13)

- 意法半导体提升手机内部保护功能,为环保充电器开路(01-26)

- 完整两节AA电池/USB电源管理器(03-18)