PCM串行数据流同步时钟提取设计

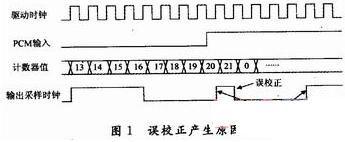

(2)在同步时钟相位出现很大偏差时,若PCM输入信号在某全局时钟上升沿过后很短时间到来,同时分频计数器输出同步时钟上升沿随后出现,接收系统将对该码元进行一次采样,此时,若紧随其后的全局时钟上升沿检测到该PCM信号上升沿且计数器count2值为21,就会误校正输出同步时钟相位,出现如图1所示情况,同步时钟上升沿在本码元内出现两次,一个PCM输入高电平码元被采样两次,产生接收错误。

上述两种情况中,出现第一种会造成采样错误影响信号的后续处理,第二种情况则会造成采样时钟相位校正错误,导致信号采样失败。

针对这两种情况,需要对基本方法进行进一步完善,设计中分别给出如下方法来解决:

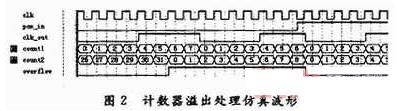

(1)针对计时计数器溢出情况,在提取模块中设置一个溢出位overflow,在count2溢出时置位为1,此时,全局时钟检测到下一个PCM输入信号上升沿时忽略计数器计数值立即进行相位校正,以推迟校正代替漏校正,达到改进系统工作性能的目的。添加该处理过程后,系统对相应情况校正结果如图2所示。图中count2计数器溢出后overflow置高电平,在遇到下一个PCM输入信号上升沿时立即校正输出时钟相位,未考虑count2中计数值为8小于20的因素。

(2)针对采样输出时钟的误校正情况,在功能模块中设置一个标志位changed,当某PCM高电平码元内已经发生采样时钟的上升沿跳变changed位置1,这时,在该码元未结束前不再进行校正,changed标志位置位后在计时计数器计数值大于20时清除。如图3所示。

经过上述的异常情况的处理程序,同步时钟提取功能模块将能够正确地从输入的PCM数据流中得到准确的具有合适相位的采样时钟输出供接收数据使用。

2 同步时钟提取过程编程实现及仿真结果

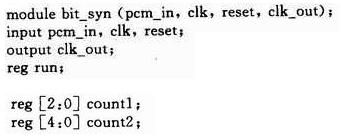

同步时钟提取模块的声明代码如下:

输入端口为pcm_in,clk和reset,分别为PCM输入信号,全局时钟输入和复位信号,输出端口仅一个,clk_out采样时钟。

模块中两个计数器count1和count2,分别为前述分频计数器和计时计数器。

三个标志位:run,changed和overflow,后两个在第二部分中详细介绍过功能,run标志位为模块工作状态标志位,run位置1模块运行;changed标记本码元采样状态,已经采样过则该位置1;overflow标记计时计数器溢出状态,已溢出则该位置1。

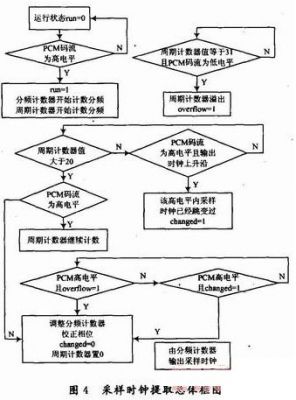

模块使用同步时序设计方式实现,所有工作在输入全局时钟信号clk上升沿的驱动下进行,包括复位功能同样为同步工作。在clk驱动下,复位信号低电位时系统复位,各寄存器进行初始化工作置初值,复位信号结束后,run标志位置1模块开始工作。系统模块框图如图4所示。

以Altera的EPM7128SLC84型CPLD作为目标器件,在集成开发环境QuartusⅡ中对上述VerilogHDL语言描述的时钟信息提取模块编译综合布局布线后进行时序仿真,得到仿真波形如图5所示。

为了方便对异常处理功能进行验证,仿真时使用输入时钟约为PCM码流速率的7.5倍,由图5中可以看出,设计对于输出采样时钟校正有很明显效果。

图6中则是使用完全8倍时钟输入的仿真结果,结果完全符合设计目标。

3 结论

本文中给出的串行数据流采样时钟提取方法及其实现,不仅局限于文中所特定语音通信PCM30/32路系统,对类似的已知速率串行数据流异步接收系统均适用。该方法能够有效地提取出数据流中包含的发送端时钟信息,并消除接收端本地时钟与之相位偏差、时钟频率偏差等因素导致的工作稳定性不高以至接收数据错误等不良结果,具有较好的适应性。

同步时钟 PCM CPLD Verilog HDL 相关文章:

- 模拟信号的原理(02-14)

- 视频编码讲坛之H.264前世今生(05-18)

- 带USB接口的PCM2702声卡制作(06-29)

- 数字音频技术知识点及声卡驱动(02-14)

- 带USB接口的PCM2702声卡的制作图解(09-26)

- 什么是PCMCIA ,什么是PC卡(07-23)