功率因数校正(PFC)的数字控制方法

能正常工作。在PFC应用中,输入电流必须跟踪输入电压,而且输出电压要保持恒定,PWM信号将在一个大的范围内变动,因此,这个问题变得更加突出。

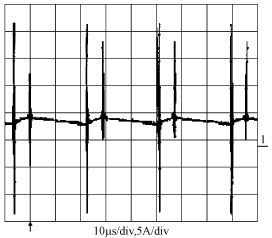

图3 存在高频噪声的电感电流

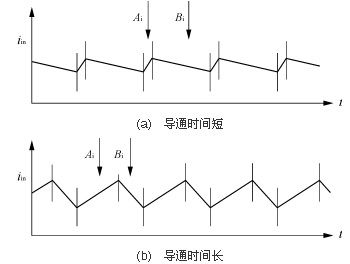

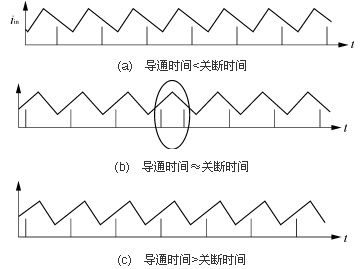

为了保证在每次开关周期中确定一个固定的采样点,而且远离开关点,一个简单的设想就是在两个尖峰之间(上升沿或者下降沿)的中点进行采样,即采样平均电流。但是,当上升沿或者下降沿非常窄的时候(即开关的占空比非常窄或者非常宽),采样信号的准确度仍然会受到开关噪音的影响。如图4所示,如果采用上升沿采样,当导通时间较长时〔图4(b)〕,采样点(Ai)是可靠的,反之是不可靠的〔图4(a)〕。为了克服这个缺点,采用改进的采样算法。这个算法同样是同步采样,但是,采样边沿的选择取决于开关的导通时间。如果导通时间大于关断时间,选择上升沿;反之采用下降沿。这样便很好地避免了开关噪声的影响。而且算法本身简单,计算量少。如图5所示。

图4 输入电流波形

图5 改进采样算法的采样瞬间

2.3 PWM信号的产生

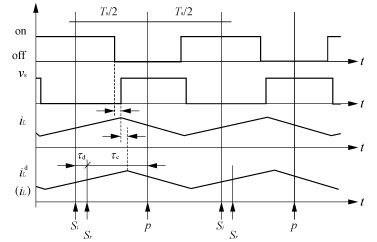

为了叙述方便,定义一个开关周期的起点p,如图6所示。对大多数数字PWM单元来说,占空比的值应该在开关周期开始之前装载入寄存器,因此,控制变量的采样应该在p点之前准备好,以便控制算法的计算及时完成。这里采用平均电流控制,选择采样点,得到每个开关周期的输入平均电流测量值。

图6 开关指令和测量输入电流iLd之间的延迟

注:信号从上至下分别为:开关指令,开关S两端的电压vs,输入电流iL,测量输入电流iLd。

理想的采样点si和实际采样点sr之间有一个时间延迟τd。τd由两个原因造成,一个是在信号链中低通滤波器产生的相移,另一个是开关S的开关指令和实际开关动作之间的延迟。这样,留给处理器完成控制计算的时间就是τc。延迟τd和计算时间τc共同决定了反馈环路的延迟。

式中:Ts为开关周期。

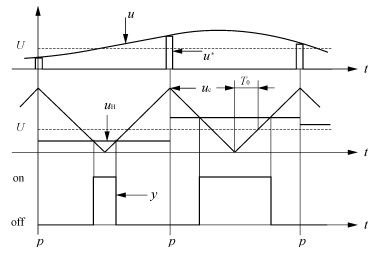

使用顶点规则采样PWM方法产生开关指令。如图7和图8所示。对于输入信号u在平衡值附近的小偏移,顶点规则采样PWM的响应可以描述为

式中:To是稳态时开关导通时间的一半。

因为,期望的电流环的带宽在1kHz到10kHz之间(开关频率为50kHz),PWM的增益趋于统一。因此,顶点规则采样PWM的传输函数可以近似为

图7 顶点规则采样PWM的原理框图

图8 顶点规则采样PWM的关键波形

注:从上至下分别是:模拟输入信号u,采样输入信号u*,

ZOH的输出信号uH,PWM载波uc,产生PWM波y

2.4 电流环和电压环的数字PI控制器

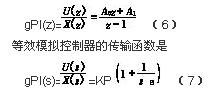

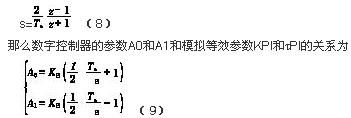

电压环和电流环都包括PI控制器。参看图1,一个数字PI控制器可以表达为

un=A0xn+A1xn-1+un-1 (5)

或者

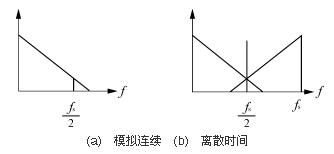

因为采样频率有限,当一个模拟转换函数采样生成离散时间函数时,如果模拟函数包含了频率高于1/2采样频率的分量,会发生重叠效应,如图9所示。

图9 从模拟函数到离散时间函数的重叠效应

为了消除高频分量(频率大于fs/2)的影响,使用Tustin规则

3 结语

在功率因数校正领域,模拟PFC控制是当前的工业选择,数字控制是今后的发展方向。将DSP控制应用到功率变换器中有很多优点,比如降低了元器件数量和成本,适应性好,产品升级方便,开发周期短等。而且随着数字控制器的广泛应用,成本有潜力变得更低。使用DSP实现数字控制,需要考虑处理器的选择,采样算法,PWM信号的产生,控制器的设计等多方面的因素。

由于DSP刚刚开始应用于控制电源,对开关整流器件采用DSP控制的研究开展的还不多,使用DSP来控制电源也存在自身独特的问题。相对于专用的集成芯片,DSP的价格高昂,而且成熟的控制算法难以获得。有限的带宽和采样频率,离散效果和处理延迟,这些因素的存在使得实时控制系统的功能需要折衷考虑。

- 超超临界机组AGC控制技术的研究与应用(06-01)

- 基于脉冲序列控制技术的降压型开关电源(10-26)

- 基于ARM的数字化控制开关直流电源设计(01-01)

- 高压变频调速技术及能量回馈技术在矿井提升机的调速和节能改造中的应用(02-07)

- 先进控制技术及应用(03-19)

- 采用数字电源还是模拟电源?(01-17)