基于ViaExpert仿真的AC耦合电容阻抗优化设计*

时间:08-14

来源:与非网

点击:

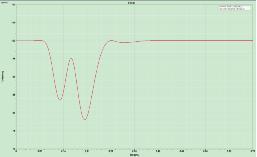

不是太大,Case2情况是最差的,因为掏空区域变小了,差分阻抗变低了。所以后续我们在PCB设计阶段就可以根据以上前仿真结果进行指导,对于通流比较紧张的情况,我们只掏空GND02层的地,对于POWER03或者ART03空间宽裕的情况下,可以掏2层处理。

4 AC耦合电容阻抗后仿真验证

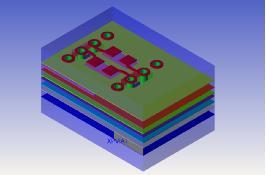

根据上节3种Case情况下的仿真结果和PCB设计的实际情况,AC耦合电容只掏空GND02层,掏空尺寸为X方向掏34mil,Y方向掏66mil。因为ViaExpert可以直接导入Brd文件,所以在PCB设计完成后在ViaExpert里面直接对Brd进行解析,提取出板上的AC耦合电容和出线。PCB实际AC耦合电容的设计以及导入到ViaExpert中提取完成的3D效果图分别如图12和图13所示。

图12 实际AC耦合电容出线

图13 实际AC耦合电容3D效果图

因为ViaExpert里面提取Brd无法获得电容相应的模型,所以后仿真需要把模型导入到HFSS中,然后加上AC耦合电容的Model,最终如图14所示。

图14 实际AC耦合电容3D效果图

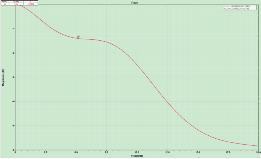

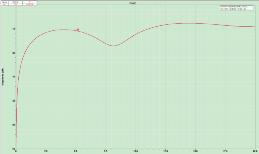

仿真结果如下图15,图16,图17所示。基本和前仿真结果一致

图15 实际AC耦合电容后仿真插入损耗

图16 实际AC耦合电容后仿真回波损耗

图17 实际AC耦合电容后仿真差分阻抗

5 结论

本文介绍了如何利用Xpeedic公司旗下的ViaExpert软件对高速串行链路AC耦合电容的前仿真差分阻抗优化以及PCB后仿真建模,前仿真得出设计方向后指导PCB设计,最后后仿真确定设计是否满足要求,最终保证高速串行链路设计的一板成功。

- 德州仪器高性能模拟运放产品系列介绍集锦(11-13)

- 如何使低功耗放大器在便携式产品中提高性能(10-03)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 高速DAC AD9712B/AD9713B的原理和应用(11-30)

- 高级设计中的高密度AC/DC电源 (01-22)

- 混频器用作开关,可使 DAC 采样频率加倍(01-22)