安森美半导体新一代PCIe方案

其特性在于具有减少EMI的扩频;启用/禁用每个输出和选择/关扩频ON/OFF的I2C接口;引脚兼容ICS841S104I。

3)NB3N3002/5573

它具有以100 MHz频率驱动NB3N106K/108K/111K的输出性能。在扇出缓冲器输出进行测量的结果显示,含25 MHz晶体的NB3N3002/5573(时钟生成器)以100 MHz模式驱动NB3N106K/108K/111K扇出缓冲器符合PCIe 1、2、3抖动及相位噪声规范;为NB3N3002/557增加扇出缓冲器不会产生足够的抖动或相位噪声以产生无法符合PCIe 1、2、3相位噪声及抖动规范的"系统"。

4)用于PCIe应用的时钟分配器件ZDB及扇出缓冲器

服务器平台有3种时钟拓扑结构:内部系统时钟、混合系统时钟和外部系统时钟。针对PCIe外部时钟架构,安森美半导体提供多种专用时钟选择,包括时钟产生器(NB3N3002/NB3N5573/NB3N51034/NB3N51054/NB3N51054/NB3N

51044) 、零延迟缓冲器(ZDB) NB3N1200K/NB3W1200L (可用于PCIe混合时钟架构),以及HCSL至HCSL扇出缓冲器(不需要精确调节时钟沿使其与ZDB输出同步的多PCIe参考时钟产生器)。

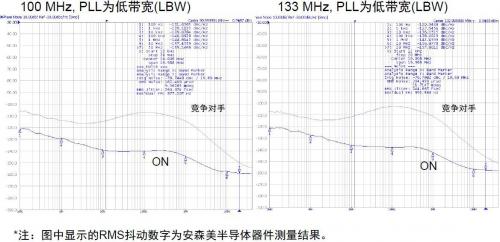

例如,NB3N1200K/NB3W1200L零延迟缓冲器(ZDB)带12路HCSL/NMOS推挽输出,特性包括:支持DIF SRC时钟;12个差分时钟输出对@0.7V (NB3N1200K) ;12个低功耗NMOS推挽输出对(NB3W1200L) ;针对100MHz和133 MHz优化,符合PCIe 第2代/第3代和英特尔QPI相位抖动规范;符合低EMI扩频;最低输入至输出延迟变化的伪外部固定反馈;每12个输出的单独OE控制引脚。两者的相位噪声均优于竞争对手,见图5。

图5:NB3N1200K与竞争器件的相位噪声性能比较

使用NB3N1200K或NB3W1200L时需注意,NB3W1200L是低能耗版本,用于要求低能耗的系统,用于长度小于20英寸的较短长度输出传输线路;NB3N1200K使用标准HCSL输出设计,在输出使用恒流源,可维持长于20英寸输出传输线路的信号完整性。

另外,多个PLL分层布置时,用户可调节带宽对时钟树进行系统优化。使用HBW(高带宽)扩频时钟时用于维持扩频特性,从而将输入与输出相位差减至最小;使用LBW (低带宽)可滤除PLL带宽内的时钟输入抖动。

以下情况应该使用ZDB或扇出缓冲器:使用零延迟缓冲器 (ZDB) (PLL模式) 时;维护同步时钟沿对齐时;当时钟生成至输出传播延迟至关重要时;用作扇出缓冲器时;当时钟生成至扇出输出传播延迟不重要时。

5)新产品

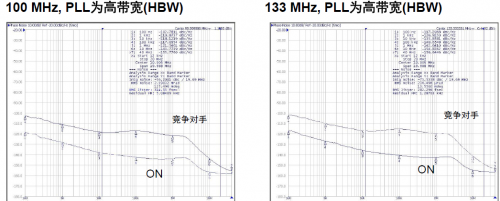

安森美半导体还在开发一系列新产品来满足英特尔白皮书规范,如带19路HCSL/NMOS报推挽输出的NB3N1900K/NB3W1900L ZDB,带8路低能耗NMOS推挽输出的NB3W800L ZDB,带HCSL输出的NB3N208K 1:8扇出缓冲器,以及带HCSL输出的扇出缓冲器NB3N106K、NB3N108K、NB3N111K和NB3N121K等。以上介绍的器件工作范围为3.3 V ± 5-10 %,工业级温度范围均为-40°C至85°C,目标市场及应用涵盖服务器(PCIe、QPI和FB-DIMM),以及网络(PCIe) 等。这些器件提供优异性能。以NB3N1900K为例,其相位噪声性能优于竞争器件,见图6。

图6a:NB3N1900K与竞争器件的相位噪声性能比较

图6b:NB3N1900K与竞争器件的相位噪声性能比较(续)

总结:

作为服务器应用及其它多种应用的时序方案供应商,安森美半导体提供包括时钟产生、零延迟缓冲器(ZDB)及扇出缓冲器等在内的完整方案。公司的产品涵盖计算机应用的宽广产品阵容,具有一流的相位噪声和抖动性能以及极高的性价比优势,符合及超越第1代、第2代及第3代PCIe要求,可以直接升级众多现有工业标准方案。

- 移动电话和PDA应用中LED照明驱动电路的设计方法(04-16)

- 移动电话、PDA应用中LED照明驱动电路的设计(05-08)

- NCP1014非隔离线路的应用解决方案(05-18)

- 160W CRT-TV电源设计指南(06-27)

- 安森美半导体高效电源管理技术助力节能环保(10-15)

- 小型LCD背光的LED驱动电路设计考虑因素(01-18)