高速信号发生应用中的关键要求

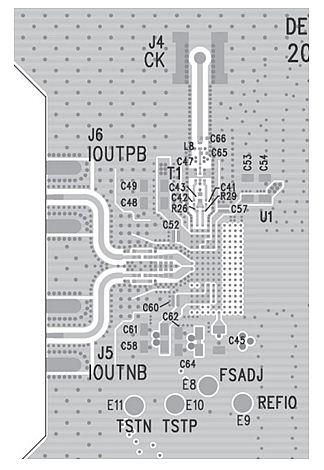

图2:LTC2000建议布局。

LTC6946是一款频率合成器,不用外部VCO就可产生从370MHz直至5.7GHz的信号。该器件具备卓越的相位噪声性能和非常低的寄生分量,适合作为信号发生应用的时钟源使用。用LTC6946驱动LTC2000高速DAC时,所产生的相位噪声足够低,适合大多数要求严苛的信号发生应用。LTC6946含有一个内部VCO,可在便利性和相位噪声之间做出权衡。如果使用LTC6945和一个外部VCO,还能实现更低的相位噪声。就LTC6945和LTC6946频率合成器而言,起主导作用的相位噪声源是VCO.在产生65MHz输出音调时,LTC2000在1MHz偏移有-165dBc/rHz附加噪声。这确保与LTC2000本身的附加性相位噪声相比,时钟相位噪声起主导作用。为了避免其他噪声导致输出信号劣化,在模拟输出电路部分应该注意使用恰当的布局方法。

恰当的RF布局

设计印刷电路板时,如果没有采用恰当的设计及布局规则,那么使用高性能DAC和时钟源的好处就会大打折扣。如果没有恰当的对称性、旁路和势垒,所产生的模拟输出波形就有可能出现误差,还可能引入噪声及其他寄生分量。图1显示了LTC2000的典型原理图。就直至500MHz的信号而言,LTC2000的噪声频谱密度好于158dBm/rHz,这有助于在很宽的信号频率范围内保持很高的信噪比。该器件的无寄生动态范围(SFDR)直至500MHz均好于74dB,而对于直至1GHz的输出频率而言,SFDR则好于68dB.为了最大限度提高LTC2000的性能,需要进行恰当的布局。DAC的输出应该作为一个差分对来对待,并尽可能以对称的路径传送。输出网络中的任何非对称性都可能导致差分信号之间出现压差。这种电压差将导致共模干扰,进而在输出频谱中产生不想要的失真和噪声。通过使每个输出的传输线实现对称性,可以避免这种干扰。

可以通过通孔以及良好的布局保护模拟输出免受干扰信号影响。信号发生DAC有3个端口,并带来了布局挑战:时钟输入、模拟输出和数据输入。如果数据输入走线靠近输出或时钟,那么数据信号会耦合到这些信号中,在输出频谱中引起杂散噪声。类似地,如果时钟信号由于不良布局而耦合到模拟输入中,就会影响所产生信号的完整性。设计电路板时,通过在数字电路、时钟信号和模拟输出电路之间设置恰当的势垒,可以使DAC实现最高性能。恰当的做法是,在不同的层上传送数字信号、时钟信号和模拟输出,以最大限度降低这些信号之间的相互影响。图2显示了LTC2000的布局,同时显示了怎样隔离数字信号、时钟信号和模拟输出。在该图中,数字走线布设在电路板内层上,仅通过通孔连接到LTC2000焊盘。时钟走线非常短,由通孔包围以隔离信号,而且不会布设在数字走线或模拟输出旁边。输出走线要尽可能对称,并由保护模拟输出免受干扰信号影响的势垒包围。遵循这些布局指导原则并采用干净的采样时钟,LTC6946和LTC2000就能产生非常干净的波形,满足要求最严苛的信号发生应用的需求。

- 精密电源的设计及心得分享(07-16)

- 德州仪器高性能模拟运放产品系列介绍集锦(11-13)

- 如何使低功耗放大器在便携式产品中提高性能(10-03)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 高速DAC AD9712B/AD9713B的原理和应用(11-30)

- 混频器用作开关,可使 DAC 采样频率加倍(01-22)