模拟IC自动测试系统的直流参数测试单元

集成电路(Integrated Circuit,IC)测试技术是集成电路产业中不可或缺的重要组成部分,而测试设备是IC测试技术的一种重要工具。模拟IC自动测试系统是一款针对模拟IC直流参数和交流参数进行测试的设备,主要用于IC晶圆的测试,以便验证芯片的性能参数是否符合规范要求。

1模拟IC自动测试系统结构

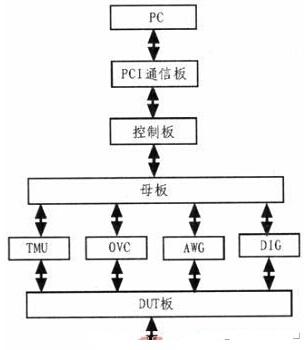

模拟IC自动测试系统主要包括PC、PCI通信板、控制板、母板、TMU板、OVC板、AWG板、DIG板和DUT板组成,系统结构框图如图1所示。

图1 模拟IC自动测试系统框图

1. 1 PC模块

PC是整个模拟IC自动测试系统的主控制中心,类似于人类的"大脑",主要负责向各个功能板发送功能指令使其实现相应的功能,并接收、处理测量得到的数据结果。

1.2 PCI通信板模块

PCI通信板主要负责对PC发送的功能指令进行译码,然后转换成测试数据总线传递给模拟IC自动测试系统,类似于PC与自动测试系统之间的"桥梁"。

1.3控制板模块

控制板主要是将PCI传递的测试数据总线进行相应的数据处理,完成PCI和各功能板之间的通信。

1. 4母板模块

母板类似于控制板和各功能板之间的"桥梁",主要实现测试数据总线的传递。

1.5功能板模块

TMU(Time Measure Unit),时间测量单元,主要功能是测量信号的频率、周期、上升沿时间、高脉冲时间等时间参数;AWG(Arbitrary Waveform Generator),任意波形发生器,主要功能是可以产生任意的波形;DIG是数据采集卡,主要对波形的数据进行采集、处理、存储和传输;OVC(Octal Voltage/Current),直流参数测试单元,主要功能对直流参数进行测试。

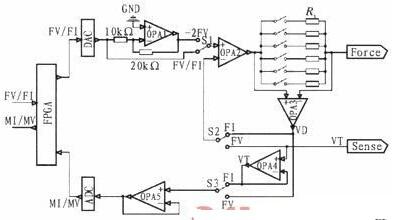

2直流参数测试单元

模拟IC自动测试系统中直流参数测试单元的主要功能是为芯片提供稳定的电压值或者电流值,然后测量其电流或者电压,从而判断芯片是否符合规范要求。本设计中的直流参数设计单元(OVC)可提供4个独立的PMU(Precision Measure Unit,精密测量单元),最大输出电压可达到+20 V,误差为0.5%,最大输出电流可达到±0.5 A,误差为0.1%,OVC的硬件结构如图2所示。

图2 OVC硬件电路结构

2.1直流参数测试单元原理

OVC系统采用16位DAC7744、16位ADC974以及开尔文连接法来提高系统的精度。PMU可以实现两种功能:FVMI(加电压测电流)功能和FIMV(加电流测电压)功能。两种功能的原理框图如图3所示。

图3 PMU功能原理图

从PC端发送功能指令FV/FI,FPGA对功能指令进行解码,从而控制DAC、继电器开关和ADC,最终将测量结果MI/MV上传到PC端。本设计中DAC采用16位的DAC7744,ADC采用16位的ADC974,它们都拥有4个独立的通道,可提供4个独立的PMU通道,分辨率为305μV,能够满足系统高精度的要求。2.2加电压测电流(FVMI)功能原理

加电压测电流功能主要是为待测器件施加一个稳定的电压值,然后测量流经待测器件的电流。将图3中的开关S2、S3打到FV端,整个电路就可以实现加电压测电流(FVMI)的功能。

首先,为了提高系统的精度,图3中的Force端和Sense端采用开尔文连接法,最终连接到待测器件的同一端。

其次,FPGA接收到PC的功能指令,当前系统实现加压测流的功能,FPGA控制DAC输出所施加的电压值,由于DAC7744输出电压范围在-10~+10 V之间,如果所施加的电压值在-10~+10 V之间,那么开关S1直接打到FV/FI端,如果所施加的电压值在+10~+20 V或者-20~-10 V之间,那么开关S1需要打到-2F V端,将DAC的输出电压经过OPA1反相放大2倍后输出所要施加的电压值。

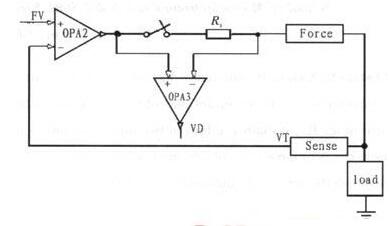

然后,DAC输出的电压值到达功率放大器OPA2,此时选择合适采样电阻Rs,并将与其相连的继电器闭合。那么,OPA2、采样电阻、待测器件就形成了一个回路,如图4所示。

图4 FVM1功能原理图

由图4可知,流经待测器件load的电流与流经采样电阻Rs的电流相等,而仪表放大器OPA3的输出电压VD是采样电阻Rs两端的压差,那么VD除以采样电阻阻值Rs得到的电流值I即为流经采样电阻Rs的电流值,也就是流经待测器件load的电流值。VD经过ADC转换成16位数字信号,上传到PC,PC端将数据进行处理,最终得到电流值MI.

2.3加电流测电压(FIMV)功能原理

加电流测电压功能主要是为待测器件施加一个稳定的电流值,然后测量待测器件的电压值。将图3中的开关S2、S3打到FI端,整个电路就可以实现加电流测电压(FIMV)的功能。

首先,为了提高系统的精度,图3中的Force端和Sense端采用开尔文连接法,最终连接到待测器件的同一端。

其次,FPGA接收到PC的功能指令,当前系统实现加流测压的功能,此时需要选择合适的采样电阻值Rs,由FPGA控制DAC输出一定的电压值,电压值等于所施加的电流值FI乘以采样电阻阻值Rs.

然后,DAC输出的电压值到达功率放大器OPA2,此时与采样电阻Rs相连的继电器闭合。那么,OPA2、采样电阻、OPA3和待测器件就形成了一个回路,如图5所示。

模拟IC 自动测试 直流参数测试 OVC FVM1 相关文章:

- 如何选择基准电压源?(02-18)

- 模拟IC基础学习:模拟IC电路设计问题(07-27)

- 利用放大器优化模拟IC极限性能设计(09-11)

- 用放大器进行模拟IC极限性能设计优化(05-21)

- 专用晶圆加工工艺实现高性能模拟IC(02-15)

- 善用放大器进行模拟IC极限性能设计优化(04-03)