用于±10 V输入的单电源、完全隔离式数据采集系统

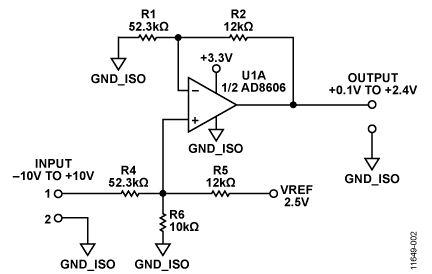

图2.输入电压信号调理电路

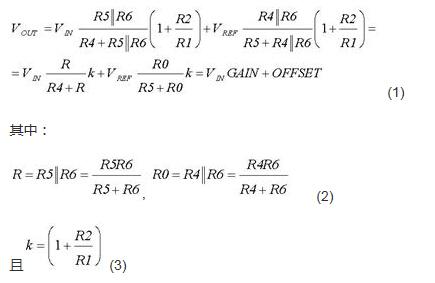

传递函数通过叠加原理求得。

增益、输出失调和电阻值的计算

若输入电压范围为±10 V,则计算如下。

电路的增益为:

由等式4可知,对于k =1.23(该值可变动,具体取决于标准数值电阻R1和R2的值),R4/R的比值可计算如下:

R4 = 9.696R (8)

由等式7可知,若VREF = 2.5V且k =1.23,则R5/R0的比值可计算如下:

R5 = 1.46R0 (9)

由等式2中的电阻R和R0,以及等式8和等式9中的比值可知,R4/R6比值可计算如下:

R4 = 5.346R6 (10)

由等式8、等式9和等式10可知,电阻R4、R5和R6可计算如下。例如,若选择R6 = 10 kΩ,则R4 = 53.46 kΩ,R5 =12.3 kΩ。

在实际电路中,为电阻R4和R5选择了最接近现有标准的电阻值。所选值为R4 = 52.3 kΩ,R5 = 12 kΩ。注意,R1 = R4,R2 = R5.

如果仔细选择这些值,因使用替代标准值电阻导致的总误差可降至几个百分点以下。然而,应通过等式1来重新计算U1A运算放大器在±10 V输入下的输出,以确保维持所需裕量。

这类电路的绝对精度主要取决于电阻,因此,需要进行增益和失调校准,以消除因替代标准值电阻和电阻容差导致的误差。

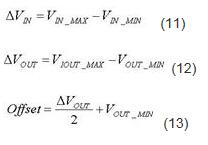

计算不同输入范围的电阻

对于±10 V以外的输入范围,可完成下列计算步骤。

定义输入范围、输出范围和失调:

计算增益:

用等式2中定义的数值替换等式17和等式18中的R和R0,并求解两个等式,得出R4/R6比值。

选择电阻R6的值。通过R4/R6比值算出R4.得到R4和R6数值,通过等式2和R4/R6比值计算R5.通过等式16计算R2和R1.可适当选择R1 = R4并计算R2.

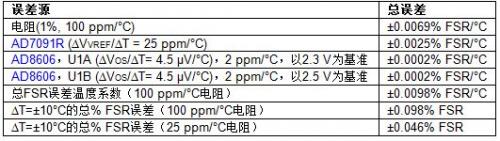

电阻温度系数对总误差的影响

公式1表明,输出电压与以下五个电阻相关:R1、R2、R4、R5和R6.TP1处的满量程输出电压对这五个电阻中每个阻值的微小变化敏感,其灵敏度通过仿真程序计算。电路的输入电压为+10 V.计算得到的各灵敏度为SR1 = 0.19、SR2 = 0.19、SR4 = 0.39、SR5 = 0.11、SR6 = 0.50.假设各温度系数以和方根(rss)方式组合,则采用100 ppm/°C电阻时,总满量程漂移约为:

满量程漂移=

= 100 ppm/°C√(SR12 + SR22 + SR42 + SR52 + SR62)

= 100 ppm/°C√(0.192 + 0.192 + 0.392 + 0.112 + 0.502)

= 69 ppm/°C

69 ppm/°C的满量程漂移对应于0.0069% FSR/°C.使用25 ppm/°C电阻可将漂移误差降低至0.25×69 ppm/°C = 17 ppm/°C,或者0.0017% FSR/°C.

有源元件温度系数对总误差的影响

AD8606运算放大器和AD7091R ADC的直流失调由校准程序消除。

ADC AD7091R内置基准电压源的失调漂移典型值为4.5 ppm/°C,最大值为25 ppm/°C.

AD8606运算放大器的失调漂移典型值为1μV/°C,最大值为4.5μV/°C.

U1A AD8606输入导致的误差以2.3 V输出范围为基准,因而为2 ppm/°C.U1B基准电压缓冲器导致的误差以2.5 V为基准,同样约为2 ppm/°C.

总漂移误差结如表1所概括。这些误差不包括AD7091R的±1 LSB积分非线性误差。

请注意,如果采用50 ppm/°C或100 ppm/°C电阻,则总漂移的最大来源是电阻漂移,有源元件产生的漂移可忽略。

表1.温度漂移导致的误差

两点校准前后的测试数据

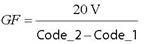

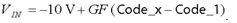

为了执行两点校准,先向输入端施加-10 V的电流,并将ADC输出代码记为Code_1.然后,向输入端施加+10 V的电流,再将ADC输出代码记为Code_2.增益系数通过下式计算:

现在,可通过下式计算与任何输出代码Code_x对应的输入电压:

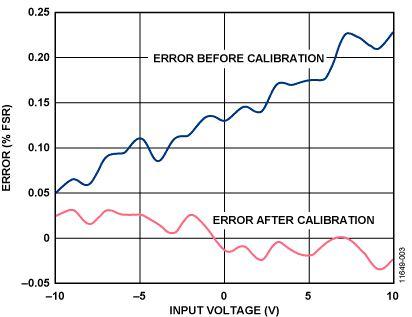

通过比较使用元件标称值计算得到的理想传递函数和未校准实际电路传递函数,可以得到校准前的误差。实测电路所用电阻的容差为±1%.测试结果不包括温度变化。

图3中所示为环境温度下校准前后的百分比误差(FSR)测试结果。如图所示,校准前的最大误差约为0.23% FSR.校准后,误差降至±0.03% FSR,大致相当于ADC的1 LSB误差。

图3.室温校准前后的电路测试误差

PCB布局考虑

在任何注重精度的电路中,必须仔细考虑电路板上的电源和接地回路布局。PCB应尽可能隔离数字部分和模拟部分。该系统的PCB采用简单的双层板堆叠而成,但采用4层板可以得到更好的EMS性能。有关布局和接地的信息,请参见MT-031指南;有关去耦技术的信息,请参见MT-101指南。AD8606的电源应当用10μF和0.1μF电容去耦,以适当抑制噪声并减小纹波。这些电容应尽可能靠近相应器件,0.1μF电容应具有低ESR值。对于所有高频去耦,建议使用陶瓷电容。电源走线应尽可能宽,以提供低阻抗路径,并减小电源线路上的毛刺效应。

ADuM5401 isoPower集成式DC/DC转换器要求在输入和输出电源引脚上进行电源旁路。请注意,引脚1与引脚2以及引脚15和引脚16之间需要低ESR旁路电容,这些电容应尽可能靠近芯片焊盘。为了抑制噪声并降低纹波,至少需要并联两个电容。针对VDD1和VISO,推荐的电容值是0.1μF和10μF.较小的电容必须具有低ESR,建议使用陶瓷电容。低ESR电容末端到输入电源引脚的走线总长不得超过2 mm.如果旁路电容的走线长度超过2 mm,可能会破坏数据。考虑在引脚1与引脚8及引脚9与引脚16之间实现旁路,除非两个公共地引脚靠近封装连在一起。

- 运算放大器的选择(03-18)

- 运算放大器的输入级(03-18)

- 运算放大器电路固有噪声的分析与测量(第二部分):运算放大器噪声介绍(05-12)

- 运算放大器电路固有噪声的分析与测量(第二部分):运算放大器噪声介绍(二)(05-12)

- 运算放大器电路的固有噪声分析与测量(07-14)

- 揭示运算放大器未来发展趋势,创新技术带来电子设计新变革(11-27)