基于KAI-01050 CCD功率电路的驱动方案

2.4电子快门驱动电路

KAI-01050 CCD为防止强光溢出提供一种结构可实现溢出保护和曝光时间可调节。溢出保护功能通过加在器件衬底的直流电压来实现,若足够大的电压脉冲(峰值为29~40 V)加到衬底,所有光电二极管内电荷被抽空,随后开始光积分阶段,实现电子快门功能。

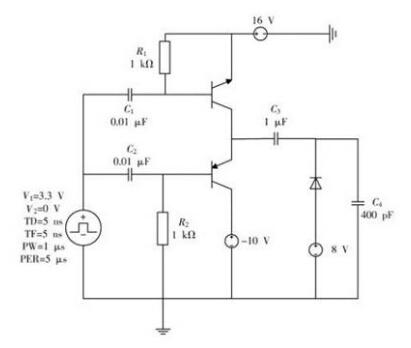

KAI-01050的电子快门电压要求如图4所示,要求加到衬底上的直流电压为VSUB,VSUB的典型值为VAB,每个CCD芯片VAB可能不同,标注在CCD的包装上,为5~15 V之间的值,在电子快门期间衬底上的电压瞬间变为VES(电压值为29~40 V),电压脉冲的最小宽度为1μs.如果采用通常的CCD驱动电路,很难实现这样高电压、窄脉冲信号,为此设计采用两个互补高速三极管轮流开关工作来实现高压脉冲电子快门信号的驱动。原理如图5所示电路,此电路中暂设VAB为8 V.

图4 KAI-01050

首先时序发生单元的时序信号经过电容C1和C2耦合到两个电阻钳位端,两个电阻R1和R2用于把电容耦合过来的信号钳位到固定的电平。这样产生的两个信号就用于控制两个开关三极管的导通与截止。两个互补的三极管的集电极接在一起作为开关输出。当加在Q2基极的控制信号向上摆动时,三极管Q2就会导通,而这时加在Q1基极的信号恰处在高电平期间,因而三极管Q1截止,所以输出到负载C3的信号为低电平。同理,当加在Q2基极的控制信号为低电平时,三极管Q2截止,而这时加在Q1基极的信号恰以高电平向下摆动,因而三极管Q1导通,所以输出到负载C3的信号为高电平。

因此,这两个三极管组成的电路为反相驱动电路。驱动电路输出经电容C3耦合到D1的钳位电路,D1的作用是将输出信号的低电平钳位到VSUB(本电路中取值为8 V)。经钳位电路后产生最后的电子快门信号。

图5 电子快门功率驱动电路

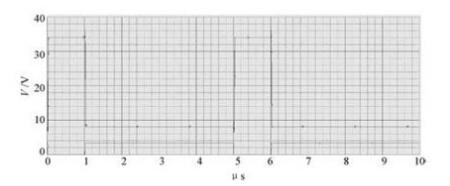

利用Cadence软件集成PSpICe工具对图5所示的电路进行仿真,仿真的输入波形高脉冲宽度选择为电子快门要求的最小宽度1μs.为看到仿真波形的细节,输入波形的周期(为电子快门的周期,在实际使用中为可调周期)选择较短的20μs.钳位电压VSUB取值为8 V,可以取5~15 V之间的任何值,实际中以CCD器件包装上标注的VAB值为准。CCD电子快门输入管脚的等效负载电容为400 pF,为验证此电路驱动能力是否满足要求,此电路中加如了容值为400 pF的C4模拟CCD的等效电容负载。仿真结果如图6所示。

图6 电子快门功率驱动电路仿真波形

图中下方曲线为输入波形,上方曲线为输出波形。

由输出波形可知,高脉冲宽度与输入一致,未出现失真,低电平为8 V,高电平为34 V,满足29 V≤VES≤40 V的要求。

3实验测试

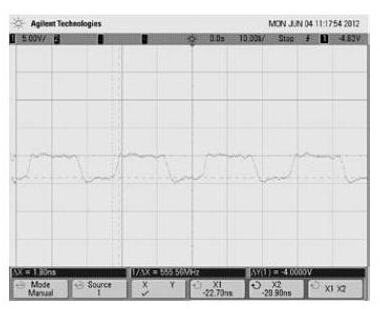

根据以上原理,设计了KAI-01050的驱动电路,并进行了测试。图7为水平转移时钟的测试波形图,驱动信号频率为40 MHz,幅值-4~0 V,上升沿与下降沿时间仅为1.8 ns左右,符合CCD驱动时序要求。

图7 水平转移时钟的测试波形图

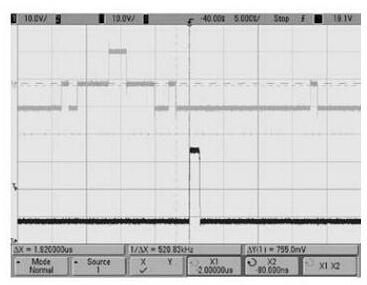

图8 三电平转移时钟和电子快门信号波形

图8为三电平垂直转移时钟和电子快门是驱动信号波形,图中上面是三电平转移时钟信号,低电平为-9 V,中间电平0 V,高电平12 V;下面波形为电子快门信号,常态电平为6.9 V左右,在计数器计数到需要曝光的时序位置时,输出一个脉冲宽度不小于1μs的29~40 V脉冲(相机设计值为32 V)。这两个信号其上升沿下降沿时间都很陡峭,满足驱动时序的要求。

4结语

本文首先介绍了KAI-01050 CCD驱动信号的特点,分析了其功率驱动电路的设计难点,基于本方案设计的重点和难点进行了各种CCD信号功率驱动电路的设计,并对部分电路进行仿真,验证了设计的合理性。

- 高速面阵CCD KAI-01050功率驱动电路的设计方案(一)(10-31)

- 光纤实现功率驱动PWM的远距离传送(09-16)

- 用于下一代移动电话的电源管理划分(08-28)

- CCD信号采集系统的USB接口设计(03-12)

- 基于CPLD的线阵CCD驱动电路设计(01-24)

- CCD时代将被CMOS终结?(05-17)