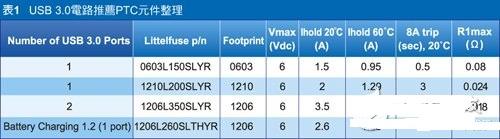

基于USB3.0电路可靠性的PTC/ESD方案

增强USB 3.0电路保护外挂ESD元件势在必行

USB 3.0增加的资料线因提供更多电气瞬变的可能入口通道,也将承受更大的ESD威胁。尽管现代晶片往往都有受到一定程度的ESD自我保护功能(通常在500~2kV的范围内),但对USB 3.0电路而言仍是不足的,因此须导入额外的ESD保护元件。

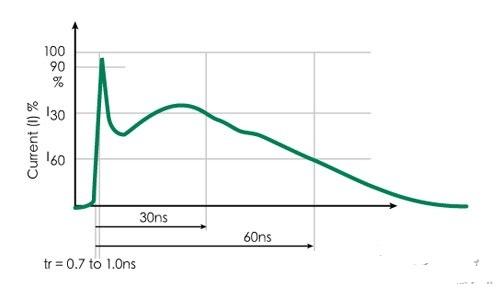

静电防护水准的等级系根据有1,500欧姆(Ω)放电电阻的MIL-STD HBM模型分级。MIL-STD模型中,以一个2kV的脉冲相当于有着330欧姆放电电阻,且电压为500伏特的IEC 61000-4-2模型为基础(图3),目前人体放电模式(HBM)可用脉冲在相同的瞬态电压是IEC模型可用的四分之一。发生静电放电事故时,电压往往高达15kV甚至更高,将导致软体故障、电路潜在损害或灾难性故障,因此,额外的ESD保护是提高现代介面埠生存能力的必要条件。

图3 IEC 61000-4-2 ESD电流波形

为确定外部ESD事故预防系统,业界已开发出几个测试标准,其中,IEC 61000-4-2条款受到最广泛的认可;该标准定义ESD在不同的环境和安装条件中的测试规范,如今的USB 3.0埠在此规范下,须承受至少8kV接触放电,达到IEC 61000-4-2条款第四级的要求。

USB 3.0拥有更高的资料速率,就特别须要注意元件的电流容量以保护电路,且系统设计人员在选择ESD保护元件时也须留意许多重要参数,包括动态电阻、箝位元电压、击穿电压、寄生电容、最大ESD能力、多脉冲能力、封装形状、关断状态的阻抗或泄漏电流、设备电路配置和布局的灵活性等。

现阶段,市场上有几种不同的防静电抑制技术,例如多层陶瓷压敏电阻(MLV),聚合物ESD抑制器和半导体的ESD抑制技术,是否选择正确的元件将决定USB 3.0埠的设计可靠度。由于ESD保护元件的电容、箝位元电压和动态电阻最为重要,一些保护元件制造商已实现以最小寄生电容提高讯号完整性的产品,同时有些产品的箝位元性能也达到最大化,但代价是电容很高。

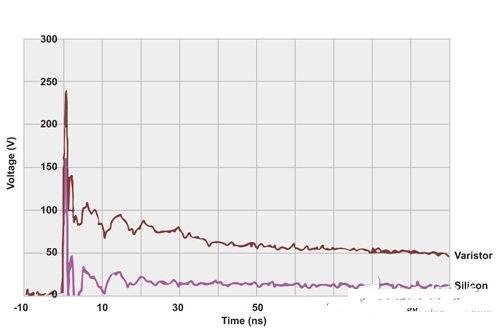

举例来说,瞬态电压抑制(TVS)二极体和二极体阵列有较低的动态电阻,提供卓越的箝位元性能,并能保持非常低寄生封装电容。图4显示矽方案的箝位元性能与MLV ESD保护技术的比较,以矽为基础的解决方案的箝位元电压更低。

图4矽电阻与压敏电阻的箝位元性能比较

TVS二极体阵列提供多通道ESD保护解决方案(图5),成为目前USB 3.0保护的最佳选择。该类元件能吸收瞬态电流,并泻放电流,同时透过雪崩或齐纳二极体箝制电压位准。如图6所示为USB 3.0静电保护方案架构图。

图5保护USB 3.0电路的TVS二极体阵列示意图

图6上为USB 3.0静电保护方案架构图

USB 3.0电路保护元件对维护资料完整性也非常重要,任何附加电容都可导致讯号失真,并降低讯号的可靠性。测试静电抑制器的寄生电容对讯号完整性影响的主要方法是进行眼图测试,此测试须重复采样数位讯号,并在示波器上显示出眼图,用来定义可接受的讯号品质和依从性。

- 基于S3C44B0X的心电血压监测仪USB接口设计(11-28)

- C8051F320在USB设计中的应用(01-18)

- 基于ISP1581型接口电路的USB2.0接口设计(01-18)

- 用CP2101将USB口扩展成串口(01-18)

- TM1300 PCI-XIO口的UART和USB接口设计(01-17)

- 基于CH371的实用USB接口设计(01-23)