LMK0480X 产品供电电源设计指导

2.2.2 不同供电管脚噪声对 LMK0480X 输出噪声的影响分析

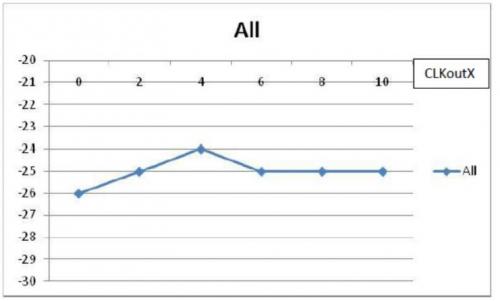

1.当干扰电源输入到所有的供电管脚,测试所有输出管脚的 PSRR。如下图所示,几乎所有输出端口的 PSRR 大约是 25dBc。

Figure 3 干扰电源应用到所有供电管脚的 PSRR 测试结果

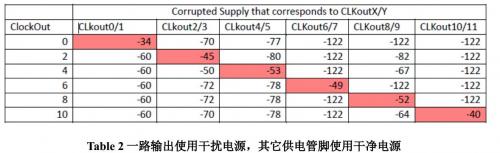

2.只将干扰源输入到 LMK0480X 其中一路输出管脚供电,其它供电管脚都使用干净的电源,PSRR 测试结果如下图;可以看到,只有使用干扰电源的那一路 PSRR 结果比较差,其它输出受到干扰电源的影响不大,都可以达到 60dBc 以上。

在没有使用干扰电源的端口加上去耦电容,继续上面的实验发现,可以发现受到电源干扰的输出端口的 PSRR 也略有改善,但仍然是最差。

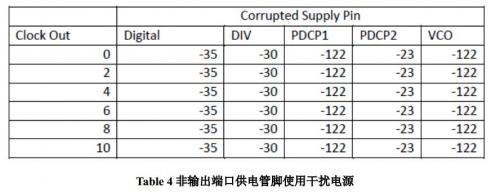

3.将干扰电压源分别输入到除输出管脚电压以外的其它管脚,例如 digital 电路部分,charge pump电流供电部分等,测试结果如下。可以发现,PDCP1 和 VCO 对于干扰电源的滤除非常明显。PDCP1 管脚主要是因为环路滤波器非常窄,对于电源干扰加以滤除;VCO 供电管脚内部集成了LDO,所以也对外部的电源干扰不敏感。通过实验可以发现,对于外部供电最为敏感的是 PDCP2和 div 的电源管脚,PSRR 分别是-23dBc 和-30dBc 。所以在实际应用当中,一定需要着重考虑PDCP2 和 div 的供电设计,供电电路上要增加磁珠,同时要确保没有< 1nF 的去耦电容,防止鉴相频率泄露到地上从而耦合到输出管脚,这对输出的杂散非常重要。

3、总结

本文主要介绍了 LMK0480X 系列时钟供电部分主要的设计需求和 PSRR 性能分析。通过实验证明,对芯片供电电源管脚的去耦设计,尤其是 PLL2 供电管脚的设计和芯片内部不同电源模块的电源隔离设计,可以显著降低 LMK0480X 系列产品的输出噪声性能,提供超低抖动的时钟输出。

4、参考资料

LMK0480X Datasheet

- 德州仪器LMK0480X holdover的功能分析(06-22)

- 一种AC/DC电源供电系统的应用新方案(05-04)

- 参量换能器收发电路设计(06-22)

- 锂离子电池用保护电路的低功耗设计(07-07)

- 一种准谐振反激式控制器功能简介 (10-27)

- SLC供电电源的设计电路(01-29)