LDO线性稳压器拓扑结构及分类

LDO线性稳压器通常被设计工程师作为辅助措施,并且经常被选用于产品开发的后期阶段。设计工程师比较关注的是如何使复杂的基频(BB) 或射频( RF )ASIC 发挥作用,而不是其所选线性稳压器的功率/性能。

线性稳压器的选择依据通常性能列表中的主要规格,而不是位于数据表封面以内的非常关键的核心和性能参数。规格经常很容易令人误解 - 封面上所列的规格只代表主要参数,但如果不与其他连接参数相结合时,便失去了价值。例如,接地电流是这些参数中的一个。出现这种情形的原因是,线性稳压器市场的竞争性质让器件制造商认识到, 需要让时间有限的工程师们更加关注自己的器件。此外,在信息提供方式方面,也没有真正的标准化。不同的数值范围、温度和负载只会使设计工程师在比较部件时导致混淆。线性稳压器

现代线性稳压器为满足具有挑战性的要求提供了许多独特的结构。基本上,线性稳压器是一个运算放大器加一个通路晶体管。运算放大器使用两个参考点,一个是内部带隙基准,另一个是输出端的电阻分压电路。在稳压过程中,电阻分压网络的电压值向运算放大器提供与带隙基准相比较的反馈。

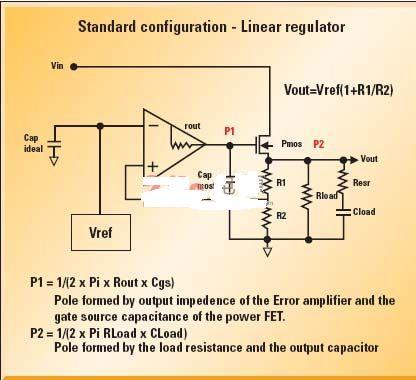

比较的结果决定了通路晶体管增加或减少导通电流。这是具有两个主极点的闭环系统,这两个主极点分别是误差放大器/通路晶体管的内部极点,以及输出电流需求和输出电容器的 ESR 构成的外部极点。这两个主导极点的处理将影响器件的性能,并会对闭环的稳定性构成主要影响(见图1)。

图1

线性稳压器分类

更高的效率是设计工程师持续的要求。这个要求就转化为对Iq(静态工作电流) 和正向电压降的降低。随着制造商提高线性稳压器的标准性能,也为其他特性带来了负面影响。

通用线性稳压器的设计可以提供最佳的整体性能。

彼此互相影响的性能指标会被折中处理。

封装选择则主要取决于成本和广泛的市场接受能力。

数字线性稳压器

数字线性稳压器设计用于支持系统的主数字核心。现代 DSP 和微控制器必须具有快速的效率以及通常较高的电流要求。

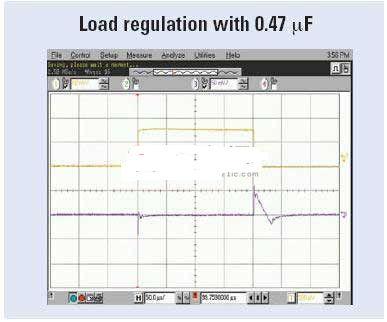

需要无线标准的新兴市场需要大量的滤波,这为数字处理核心的软件负载带来很大的压力,这将转化为对电源管理器件的高要求和快速响应。这些功能驱使着那些对于数字负载非常重要的主要特性的发展。(图2)线路和负载调整率/瞬态响应是其中首要的功能。这些参数尽管在数据表中通常不太容易找到,但可以通过两种方式来确定:V/I的偏差百分比或实际V/I偏差值。这些值应以一种负载电流为参考基准或以输入电压的变化为参考基准。

图2

电池供电的和低功率的系统具有长期的非工作时间,数字线路稳压器被设计成在这期间进入休眠状态,而在需要时可快速启动。在休眠模式期间,线性稳压器的所有主操作(包括带隙基准)将关闭。重要的是,快速开启时不能导致过冲。线性稳压器的过冲以及克服过冲的能力取决于Iq值,随着Iq值的降低,保持或改进这种能力将会更难。

我们所需的就是能够快速驱动内部电容节点,并且具有可用电流来实现这一点。随着我们进一步降低驱动内部电容节点的可用电流,线性稳压器的反应能力将随之降低。

假定我们设计了一个反应能力足够快的电路,但存在过冲现象,则克服过冲的一种方法就是通过采用电容器来阻滞过冲。结果,这将增加电容负载,并且提高Iq值的需求。

模拟/射频线性稳压器

模拟线性稳压器主要围绕着空中接口的要求驱动。

空中接口是便携式通信的最薄弱环节,因为信号对噪声和信号衰减极为敏感。因此当考虑模拟线性稳压器时,很重要的一点是,器件本身不会在所需的信号中进一步增加噪声,并且抑制其他电源的噪声。模拟稳压器需要良好的抗噪声性能(以有效值VRMS来度量)以及噪声抑制能力(以电源抑制比PSRR的dB值来度量)。

降低噪声

带隙参考和通路晶体管是主要噪声源。增加外部旁路电容器可以降低此噪声,但这会增加成本以及波形系数。也可以在硅片内增加内部电容器,因为晶体管级别的噪声实际上是以下两个因素构成的:热噪声和闪烁噪声。原因是电子相互碰撞,和Si02级别中的电子捕获。

PSRR 是器件抑制另一个稳压组件或噪声源产生噪声的能力,这在模拟环境中相当重要,因为模拟 IC 器件比数字 IC 器件对噪声更敏感。

噪声本身与接地电流具有直接相关性,因为它受晶体管驱动的影响。Mosfet 中的驱动电流越低,闪烁噪声和热噪声越差。较低的驱动又将转换为较低的 Iq 值。

因此,在选择线性稳压器时,必须查看产品详细资料以评估您的独特应用所需的整体性能。

- 如何设计一个合适的系统电源(上)(11-20)

- 如何将CMOS LDO应用于便携式产品中(01-15)

- 用低压差线性稳压器优化开关电源设计(01-18)

- LDO稳压器等效串联电阻的稳定范围(01-24)

- 低电压PLD/FPGA的供电设计(01-24)

- 拥有线性稳压器特性的下一代移动DC-to-DC转换器(02-08)