减少高速ADC系统中的数字反馈

时间:07-30

来源:凌力尔特公司

点击:

模式和随机函数发生器时 LTC2261-14 的 SFDR 性能。

Fs=125Msps,AIN= 70MHz、-65dBFS,平均 128k 点 FFT

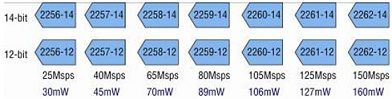

与今天市场上提供的同样采样率和分辨率的可比较 ADC 相比,LTC2261 系列 ADC 的功耗仅为其 1/3。LTC2261-14 为 14 位 125Msps ADC 仅从 1.8V 模拟电源消耗 127mW 功率,而 14 位 25Msps ADC LTC2256-14 仅消耗 30mW 功率 (参见图 7 以了解整个系列的器件)。为了进一步节省功率,还提供了打盹或休眠模式,以使功率降至 0.5mW。

图 7:超低功率 1.8V ADC 系列

LTC2261 是一款极端灵活的高速 ADC,具一个 SPI 兼容的接口,以设定和调节若干独特的设置。SPI 端口用于选择数字输出配置 (CMOS、DDR CMOS、DDR LVDS)、从 7 种 LVDS 输出电流设定值中进行选择,以根据所驱动的负载或距离决定最佳的功率要求,或启用任选的 LVDS 输出终端来帮助消减由接收器上的不良终接所引起的任何反射,从而节省了外部组件和板级空间。还可以选择测试模式,以允许用户验证 ADC 和处理器之间的连接。

结论

在采样情况下,良好布局仍然不能提供避免数字反馈所需的隔离,LTC2261 的内置功能可用来帮助抵消引发这种不良干扰的地电流。LTC2261 提供极高的灵活性和调节能力,以改善数据采集系统的性能。

- 3GSps超高速ADC系统设计解决方案(06-24)

- 用于工业信号电平的精密24位、250 kSPS单电源Σ-Δ型ADC系统(02-11)

- 16位、100kSPS逐次逼近型ADC系统(10-16)

- 评价Spice模型不能仅考虑直流与交流性能(11-26)

- 同步队列串行接口QSPI的研究与应用(09-21)

- 基于OrCAD/PSpice的信号产生电路设计(04-04)