如何解决FlexRay时钟同步的同向漂移

为有限值,而因为A的特征根有λ1=1,(I-A)是不可求逆的,所以S将含有不定值,所以随着n的增加, T(n+1)是不断漂移的。

5 漂移对系统的影响

漂移使通信时钟离标准时钟越来越远,通信时钟初始相位的负值代表它比标准时间延迟(如图1所示)。在延迟超过1个cycle时就会使上次写入的帧还未发出就被覆盖。以cycle=5 ms、100次校正漂9.3 μs计,53763次校正会漂1个cycle,这就是说,8.96 min会产生一次丢帧。由于节点都是同步的,每个slot都会发生丢帧,如果每个cycle有91个静态slot,那么意味着每8.96 min丢失91个帧--平均每6 s丢一帧。而且,如果host时钟是偏快方向漂移,那么丢帧的频度还要增大。

补偿过头时URT为负值,通信时钟将比标准时间提前。这种情况一般不会发生,因为规定选延迟的最小值作pDelayCompensation。但是这里又出现了host时钟的漂移问题:所有同步帧的内容是由host写入的,host必须在相应slot的开始前使同步帧的内容就绪。最坏情况是原来host在slot开始前写入,漂移超过了gdActionPointOffset就会产生同步帧未写入的情况。FlexRay的帧头部有一位标志null frame. indicator,当帧内容未更新时,这一位自动设为0,同步帧还是发出去,所以并不影响同步帧的个数。

6 频率校正中的问题

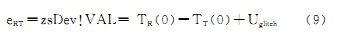

频率校正时采用了连续2个cycle的同一同步节点的相位差,将这两个相位差的差作原始数据,用类似算法计算校正量,然后按死区与限幅的方法实施校正。在同一同步节点的相位差的减法中,系统性偏差URT互相抵消,因此不引起频率的漂移。但是,在接收节点测取BSS的跳变沿时存在误差的可能性(如图1所示),BSS的跳变沿的误差直接影响到倒推ActionPointOffset的位置,从而进入eRT:

式中Uglitch为毛刺造成的误差,奇数cycle和偶数cycle的Uglitch可能是不同幅值和符号的。BSS的跳变沿是在经滤波后的zVotedVal上采取的,毛刺长度小于3个位采样周期时被滤掉,大于3个位采样周期时就可以见到。毛刺的存在位置有如下几种可能:

① "0"毛刺在TSS之前,真正TSS的跳变沿被解读为BSS中的跳变沿。此时读到的相位差较大,但是后续BSS以及其它的帧检查会发现此帧有接收错。

② "1"毛刺在TSS之中,毛刺的1/0跳变沿被解读为BSS中的跳变沿。此时读到的相位差比上述情况小,同样可检查出有错。

③ "0"毛刺使BSS内的跳变沿提前,或"1"毛刺使BSS内的跳变沿推后,当提前或推后的量较大时,后续BSS以及其它的帧检查会发现此帧有接收错。

④ 毛刺使BSS跳变沿变化量小于0.5位时,后续BSS以及其他的帧检查不会发现此帧有接收错,所以此帧会被用于时钟同步。

一个接收节点在同一cycle里受到毛刺干扰而造成有几个同步帧受影响是可能的。此时尽管有最大最小频率差的丢弃,毛刺造成的误差仍可能要进入校正量的计算。

易于导出频率校正的状态方程,它与(4)式的形式类似。因此FlexRay的频率校正可使簇内的频率趋于一致,但是仍有频率相对于标准值漂移的可能性,此漂移的方向是不定的,受毛刺出现的情况而变。

参考文献[6]进行了FlexRay的频率校正的软件仿真试验,对节点频率作阶跃变化、斜坡变化的试验结果是令人满意的。但是它并未考虑过毛刺影响。

7 时变传递矩阵的漂移

如(5)式所示的传递矩阵还有非常多的形式,由于FlexRay在选取作校正计算时要用丢弃排序后的最大最小二个误差,实际采用的同步节点的可能性组合很多。例如对4个同步节点的簇,对每个同步节点(矩阵A的一行)将有6种可能的系数,整个簇的传递矩阵A将有64=1296种可能。对矩阵A求特征根时可以发现它们都有λ=1的临界稳定的特征根:实际上每行系数的和都等于1,在用行列式求特征根时就可以将λ-1提出来。而由于FlexRay在每次排序后选中的同步节点可能不同,传递矩阵是时变的,那么是否还有漂移呢?为此按照算法作了含有排序的程序,这是相位校正的算法(不含频率校正的非线性部分)。

8.结语

FlexRay采用分布式时钟的本意是强化对抗失效的能力:有F个同步帧发送节点失效时,只要同步帧发送节点为3F+1个,簇内的时钟仍是正确同步的,因此可以保证簇内的正常通信服务。但是根据本文的动态分析,时钟相位会由于延迟补偿误差而漂移,与真实时钟有频差。这种延迟补偿误差是无法消除的,而已有频率校正方法无法发现通信时钟对真实时间的频差,因此通信时钟会与host的时钟越离越远,导致发送帧被新帧覆盖,或者时隙到达时消息尚未就绪。这些漂移引起的出错发生频率是相当高的。

由于毛刺引起的频率漂移可以用死区算法克制,但是其他各种毛刺的情况会

- FlexRay总线控制器和 TCl796的MLI接口设计(11-27)