基于FPGA的RFID板级标签设计与实现

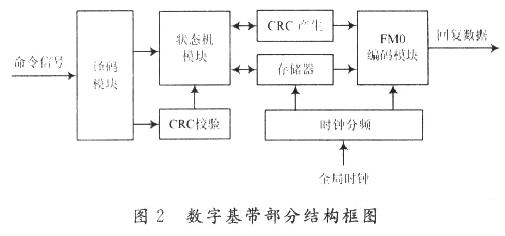

据,并发送到CRC校验模块和状态机模块。CRC校验模块对收到的命令进行完整性校验,若确认为有效命令,则触发状态机模块,控制标签执行相应操作,如读写存储器、防冲突控制等。处理完成后,则将要发送的数据送至CRC:产生模块产生相应的CRC校验码,然后将要发送的数据和校验码一起送至编码模块,最后由编码模块以特定的脉冲形式发送给模拟部分进行处理后,再采用射频技术发送给读写器。

4 测试结果

QuartusⅡ6.0是Altera FPGA/CPLD的综合性集成设计平台。该平台集成了设计输入、仿真、逻辑综合、布局布线与实现、时序分析、芯片下载与配置、功率分析等几乎所有设计流程所需的工具。Verilog HDL程序在QuartusⅡ6.O环境下编译、仿真和下载,板级标签经过总体设计、PCB板设计与实现、代码设计、仿真与下载,以及系统调试后,能够与支持ISO18000-6C标准的读写器(Cetc7 Rlid Reader V 1.O)进行通信,快速准确地收发信息,并实现防冲突功能。图3显示板级标签能够解码来自阅读器的命令信息,在状态机的控制下,正确地输出FM0编码信号。图4显示板级标签能够支持ISO18000-6C标准的阅读器正确读取(读取到的EPC码与标签一致),读取效果良好(73次/10 s),读取性能稳定。测试表明,板级标签能够实现ISO18000-6C标准中的读写功能,标签工作性能稳定,可靠性都能达到预期的效果。

5 结 语

根据ISO18000-6C标准,采用EP1C6Q240FPGA以及模拟射频分立元件,经过总体设计、PCB板设计与实现、代码设计、仿真与下载,以及系统调试后,完成了基于FPGA的板级标签的软、硬件设计与实现。该系统通过测试,已能够正常工作,读写性能优异,并实现了防冲突功能。在此基础上可以进一步提高其安全性和可靠性,所设计的标签数字电路RTL代码能够直接应用到标签芯片开发中,为下一步设计出符合该标准的电子标签芯片提供了有力的保证。

作者:邓方东,谢泽明,伍继雄/华南理工大学,中国电子科技集

- RFID标签测试技术浅析(06-26)

- RFID标签各种测试与测量方法(07-05)

- 无源UHF RFID标签的低成本阻抗匹配网络设计(12-12)

- RFID多标签阅读时防碰撞技术(11-29)

- 纸基RFID包装箱标签天线设计(01-25)

- 基于WiFi和RFID定位技术的电子标签定位算法(01-06)