航天地面测试中1553B-PCI接口转换技术实现

4 是 专用的PCI 协议芯片,所以它的PCI 端可以直接通过插卡上的引线和PCI 插槽连接。

9054 的本地端和1553B 总线控制器HOST 端通过FPGA 实现逻辑转换。9054 支持三种传 输模式,即主模式、从模式和DMA 模式,DMA 模式适合突发的大量数据的传输,由于1553B 总线的数据速率为1Mbps,数据量很小,因此采用从模式中的单周期读写模式,相对于主模式而言电路设计和时序控制也相对简单。

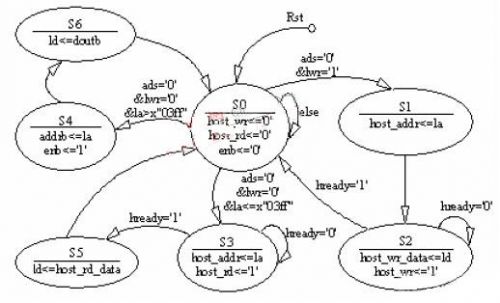

根据9054 从模式下单周期读写时序、1553B 总线控制器HOST 端时序和双口RAM 时序采 用如图2 所示的状态机实现PCI 总线对1553B 总线控制器和双口RAM 空间的读写操作。

图2 状态转换图

当9054 的局部总线复位信号有效后,状态机进入S0 状态,当启动本地总线的单周期写 操作时,在检测到地址选通信号有效,且写信号有效后,状态机进入S1 状态,将本地地址 总线赋给1553B 总线控制器的地址总线,状态机进入S2 状态,将本地数据总线赋给1553B 总线控制器的数据总线,直到数据写入后,状态机重新回到S0 状态;当启动本地总线单周 期读操作时,在地址选通信号有效且读信号有效后判断本地地址总线,当本地地址大于等于 1024 时,访问双口RAM 的B 端口,当本地地址小于1024 时,访问1553B 总线控制器内的寄 存器,这样做的好处是防止对双口RAM 操作时出现读写冲突的问题。

3.5 接口卡外围电路

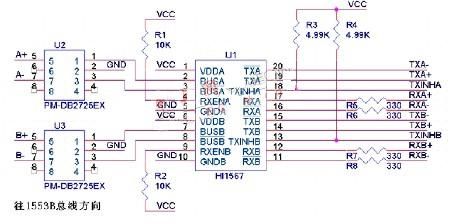

接口卡外围电路主要包括收发器、变压器和 RT 子地址电路等。收发器分为接收和发射两部分,接收部分的功能是将 1553 总线上传输的双极性差分曼 彻斯*转化为适合FPGA 输入的互补CMOS/TTL 电平。发射部分是接收部分的逆过程, 它将互补的CMOS/TTL 电平转为适合1553B 总线传输的双极性差分曼彻斯*。本设计收 发器采用HOLT 公司的HI1567,由于HI1567 的工作电压是5V,在与IO 电压非5V 的FPGA 互联时需要串接330 欧姆的电阻。

接口卡通过短截线与 1553B 主总线相连。在短截线和收发器之间需要设置隔离变压器,以提供总线驱动电压,防止终端因短路引起损坏和接口卡产生的噪声影响1553B 主总线上的信号。短截线与1553B 主总线的连接方式有两种:直接耦合和变压器耦合。直接耦合是 直接将短截线连接到主总线。变压器耦合在直接耦合的基础上加了一个耦合变压器,对终端实行两级隔离,增加了数据传输的距离,同时提高了系统的可靠性。直接耦合短截线的长度 最大为1 英尺(约0.3 米),而变压器耦合方式短截线最大可以达20 英尺(约6 米)。

本文 变压器采用HOLT 公司的PMDB2725EX,该变压器提供两种变压比,即1:2.5 和1:1.79,分 别适应直接耦合和变压器耦合两种方式。需要注意的是无论采用哪种方式,都必须在1553B 总线和变压器之间串联隔离电阻对总线进行短路保护。收发器和变压器电路如图3 所示。 RT 子地址不仅可以通过板卡上的手动开关来完成1553B 总线终端RT 地址的设置,也 可以通过上位机进行软件设置。

图 3 收发器变压器电路图

4 驱动及应用软件设计

驱动程序的基本功能是完成设备的初始化、对端口的读写操作,中断的响应以及调用。 本文采用DDK(驱动程序开发包)来编写驱动程序,这里就不做详细介绍。 应用软件采用 Visual C++编写,完成对PCI 的读写操作,进而实现控制1553B 总线的数据传输。其中,BC 模式下的流程为:

(1)读取自检寄存器,判断工作状态;

(2)通过配置寄存器,设置工作模式为总线控制器(BC);

(3)根据中断条件设置中断使能寄存器;

(4)初始化中断队列;

(5)定义BC 块和发送接收数据缓冲区;

(6)将控制字、命令字和需要发送的数据写入相应的消息块中;

(7)设置控制寄存器启动传输;

(8)轮询中断状态寄存器,如果中断,进入中断程序,处理相应的中断。

5 结束语

为实现有效载荷地面测试过程中终端设备与星上1553B总线上被测试设备之间的信息交互,需要应用1553B总线到计算机标准接口的通信板卡。本文通过对1553B总线和PCI总线协议的分析,结合航天地面测试实际要求提出了一种1553B-PCI总线接口卡的实现方法,给出了硬件结构框图,部分原理图和接口控制的FPGA实现。经过测试,实现了计算机通过PCI总线与远程终端设备的信息交互,满足了实际要求,并在XXX型号地面测试中应用。

- 基于ISP1581型接口电路的USB2.0接口设计(01-18)

- TM1300 PCI-XIO口的UART和USB接口设计(01-17)

- PC机扩展RS-232接口(01-25)

- LVDS接口电路及设计(01-26)

- 基于RTL8019AS的串口与以太网接口转换器(04-29)

- 串行及并行A/D转换器在高速数据采集中的采样差别性分析(05-19)