在高清显示器上优化标清视频

如果同时添加两个帧,每个像素的色度信息抵消,而亮度像素数据加倍。同样,如果前一帧减去当前帧,亮度像素数据抵消,而色度信息加倍。

尽管3D梳状滤波处理存在很多优势,但设计人员仍必须解决其性能局限性和一些挑战。3D梳状滤波器能让图像的亮度和色度完美分离,而传统的2D梳状滤波器或陷波滤波器达不到这种效果。

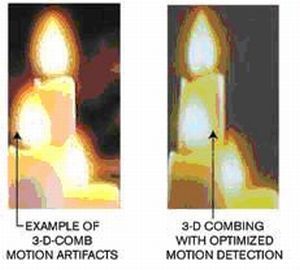

但是,只有图像中的像素绝对静止时,才可以实现亮度和色度的完美分离。反之,如果图像在移动,两个连续帧的像素数据也在发生变化,便无法使用3D梳状滤波器(图10)。重要的是,视频解码器检查每一个像素,并与之前存储的像素数据作比较,以确定是否发生了移动,进而决定应采用哪种梳状滤波器。

图10:对移动图像进行梳状滤波会产生明显的伪像。

由于移动检测比较复杂,采用的方法必须能分析当前和存储帧的每个活动像素,以便确定使用哪种方法来分离信息。

3D梳状滤波技术梳理静止像素,2D梳状滤波技术处理无复杂运动的区域,而陷波滤波器进行复杂运动区域的处理。3D梳状解码器的主要挑战并非3D梳理过程本身,而是3D梳状滤波器、2D梳状滤波器和陷波滤波器之间复杂的运动检测和自适应切换。

当梳状滤波器无法胜任

自适应3D梳状滤波器依赖解码器来正确检测图像移动。否则,梳状滤波器就不能正确处理像素数据,造成运动伪像(图11)。图11a中鸟的翅膀向下。图 11b中翅膀已经向上舞动,而图11c中翅膀再次向下。这是鸟舞动翅膀的正常顺序。

图11:自适应3D梳状滤波器依赖解码器来正确检测图像移动。这是鸟舞动翅膀的正常顺序-向下(a),向上(b),再向下(c)。

许多3D梳状解码器检查帧1和帧3,结果发现帧1和帧3相同,便误认为没有产生图像移动。因此决定用3D梳状解码器来处理数据(图12)。

图12:利用3D梳状解码器,无效检测引起明显的网格伪像(a)。图像移动校正后,无网格伪像生成(b)。

与之相反,配有3D梳状滤波器的高性能视频解码器利用很多帧存储器来更准确地检测所有帧之间的运动。使用大量的帧很有必要,有助于解码器准确判断何时何地采用3D梳状滤波器。

实现更多的功能

3D梳状滤波器要正常工作,内存缓冲区需存储视频像素数据帧以便分析和处理。ADI公司的12位标清/高清电视视频解码器ADV7802之类解码器,配有 3D梳状滤波器和图形数字转换器,通过处理其它非3D梳状滤波器任务,如先进的时序降噪,最大限度地利用内存空间。

通过配备3D梳状滤波器,ADV7802采用多种技术将当前帧的像素数据与之前存储的数据进行比较,从而过滤并消除图像噪声。

外部存储器也可以实现先进的时基校正。基于帧的时基校正确保解码器总是输出固定时钟、固定的每行采样数、不变的每帧行数,以及正确的场序。

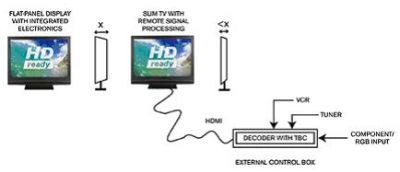

虽然电视应用通常不需要外部存储器,但是越来越多的制造商将更多的接收器和电子控制设备转移到单独的远程遥控盒中,以尽可能减小显示面板的厚度。不过这类设计也限制了需要直接与电视机相连的电缆数,这可能会造成布线困难(图13)。

图13:薄型显示器面板将接收器和电子控制设备转移到独立单元。

远程遥控盒通过HDMI(高清多媒体接口)或类似链接接入显示器。当该链接工作时,电视需要稳定的像素和时钟数据。由于时基校正允许视频解码器和链路的发射器件直接连接,因此解码器甚至能为非标准输入设备提供可靠的时序和像素数据。

除了亮度和色度分离,复合视频处理的很多其他方面也直接影响画面质量。ADC输入端的性能对显示器接收的整体视频质量起着决定性的作用。

专业品质的视频解码器(如ADV7802)利用12位ADC实现了优于62dB的信噪比。值得注意的是,对于注重性能的应用,差分相移和增益可分别超过 0.45 °和0.45%。成本敏感应用则可以采用配置9位ADC的视频解码器,如ADI公司的ADV7180。

解码器还必须能够处理非标准和微弱的广播信号源。电视用户和制造商仍旧高度重视这些要求。刚购买新型高端大屏幕等离子或液晶电视的消费者可能还会将其连接到使用了12年的录像机和模拟射频电缆系统上。

以往消费者将录像机与旧显像管电视机连接,如今他们期待高清电视能带来至少与旧显像管电视机一样好的性能水平。也就是说,录像机的视频应该稳定,即使在 "特技"模式下(即暂停、快进,或后退时)也能继续保持锁定。

微弱的射频信号也应该与颜色锁定保持同步,即使输入信号降至25dBμV以下。要解决低电平射频信号和视频信号与旧的非标准系统带来的问题,解码器设计者面临诸多挑战。

确定解码器的质量水平基准时,采用何种算法需要慎重考虑。许多制造商都纷纷推销自己能够成功地处理这些信号源。例如ADI公司的视频解码器集成了同步检测和提取、重采样和先进的后端FIFO管理等技术。

诸如ADV7802中的智能滤波算法则采用锁相回路(PLL)模块,以及水平同步(HSYNC)和垂直同步(VSYNC)处理器模块,确保正确提取同步信息。该滤波器确保解码器能够识别其查找同步信息的时期。同步锁相回路模块和处理器模块则确保所检测的同步信息正确排列。

- 视频解码器SAA7111在图像采集中的应用(06-21)

- 基于CPLD和VS1011E解码器的电梯语音系统设计(11-26)

- 基于ARM核的音频解码器单芯片系统(01-05)

- H.264解码器中一种新颖的去块效应滤波器设计(10-21)

- 应用于汽车电子的音频插孔开关(06-27)

- AMBE-2000语音压缩电路的性能及应用(07-05)