一种基于2.5G和3G蜂窝电话电源管理解决方案

用户对于自己所购买的蜂窝电话一般有许多要求,长通话时间和长待机时间显然是其中最重要的两项。尽管目前2G蜂窝电话可以通话几个小时并待机好几天,但新型2.5G和3G蜂窝产品却不能做到这样。事实上日本的早期试验发现,有些3G蜂窝电话用不到一小时就没电了。

设计人员应该认识到,解决这一问题的答案并不仅在于蜂窝电话设计的模拟部分或数字部分,要满足最终用户在功耗方面的要求,设计人员在开发下一代系统时必须有一个总体电源管理方案。本文将详细讨论系统功耗涉及的每个因素,分析设计人员将面临的电源管理难题,并介绍解决这一设计难题的一些有潜力的解决方案。

主要影响因素

在讨论具体细节之前,让我们先简要看一下蜂窝电话中必须进行电源管理的关键部分。图1是一个典型2.5G蜂窝电话设计的主要功率消耗模块。

发送功率放大器对设计工程师来说是电源管理主要难点之一,这种功率放大器要求很高峰值电流,有时将近1安培,因此该部件消耗的手机电池能量比任何其它部件都多。在通常使用情况下,功率放大器消耗的电能几乎要占电池总能量的一半。

RF收发器不如功率放大器耗电多,但也会为设计人员带来一些功率方面的问题。平均来说,收发器在发送或接收模式下消耗的电流介于50至100mA之间。

除了功耗之外,收发器还为设计人员带来另一个挑战,即从蜂窝电话其它部件电源处收到的噪声会极大地影响收发器的整体性能。因此设计人员必须隔离收发器的电源,以应付可能出现的噪声问题。

包括音频编解码器、射频编解码器和电源控制功能的模拟基带器件消耗的功率并不高,但也必须提供干净的电源才能满足手机性能要求。

除了发送功率放大器之外,数字基带器件消耗的功率最多,数字基带IC的功耗理解起来比较复杂,因为较高处理器时钟速度和晶圆工艺相关特性等导致很多此消彼长的现象。一般来说,可实现高时钟速度以满足应用要求的晶圆工艺,其关闭状态泄漏电流相对较高,这将导致因逻辑开关而形成的有源功率部分,以及无论处理器是否开关都会消耗功率的泄漏部分。

上面列出了蜂窝电话主要耗电部件,下面让我们看一下设计人员解决这些问题所使用的技术。我们从数字基带部分开始。

逻辑功能方面的问题

对于电池供电或低功耗设备,不同时期的数字信号处理器都提出过电源管理的要求,主要重点是降低有源功率,对CMOS技术来说就是信号转换以及设计中节点电容充放电引起的功耗。减少这一动态功耗部分而进行的努力一直集中在时钟控制上,因为时钟是同步系统中主要的激励源。

将系统时钟网络分割成具有自动软件控制的单独时钟域一直是控制时钟的有效途径,如今新时钟技术如动态电源和频率变换(DVFS)也用到了DSP系统中,可进一步降低有源功耗。

DVFS允许某个模块电路的工作电压在系统面临繁重处理任务时升高,从而使时钟频率和电压暂时增高。它降低系统功耗的原理是,正常情况下系统电路工作在较低电压和频率模式,仅在进行大量数据处理时才转到更快更高的功耗模式。但必须指出的是,技术发展而导致的主电源电压不断下降(从5伏到3.3伏再到1.8/1.5伏,现正走向1.2伏及更低)限制了DVFS在同步电路中真正发挥作用,因为此时最低和最高工作电压变得非常接近。

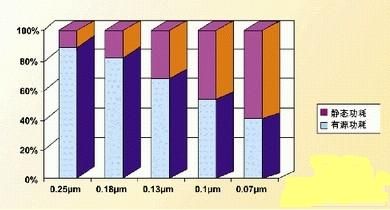

基带结构的静态功耗控制也引发了一些新的功率控制问题。因为现代CMOS技术中晶体管的静态功耗大幅增加,特别是在支持高性能操作时,这主要是由于为满足性能要求必须将几何尺寸缩小并且牺牲晶体管阈值电压,而该静态部分(或称泄漏电流)对电源电压水平很敏感。图2显示了微处理器的动态和静态功耗变化情况(使用高性能晶体管在最大电压时)。

现在还处于后期开发阶段旨在减少泄漏电流影响的新技术采用了待机(或"睡眠")系统状态,这种功率状态要么维持全部或部分系统状态,要么完全关闭。在维持状态时,可采用降低工作电压的作法,但需要在存储器和寄存器等功能中应用一些特别的偏压技术;在状态关闭时,系统必须关掉DSP中的模块,通过电气隔离这些模块以确保它们不受系统其余部分操作的影响。

功率泄漏还可作为一个指标,限制针对某个功能所构建的晶体管总数。不管是从静态还是从动态功耗的角度看,晶体管都不是没有代价的,因此必须对模块进行优化,尽可能采用最少数量的晶体管。

全局观念

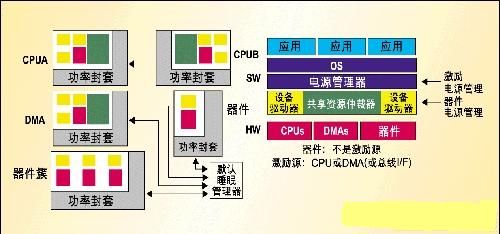

以上讨论说明,为何必须在整个基带芯片级上进行全局电源管理,将时钟和电源控制重新组合成一种硬件与软件设计人员共用且一致的模型。电源管理要求将各部分联系在一起以进行有效控制。

处理基带硬件部分时,设计人员首先必须仔细地将系统分割成采用同类功

- 用于下一代移动电话的电源管理划分(08-28)

- DC-DC电源驱动PA提高WCDMA手机发送效率(11-01)

- 3G手机电源管理的设计趋势(05-11)

- 3G无线环境下实时视频浏览技术的实现方案(03-01)

- 3G交互式视频网关的设计与实现方案(05-30)

- 物联网商机大 M2M应用于3G市场开始起飞(12-20)