基于Multisim 9的数字电子钟设计与仿真

数字电子钟是用数字集成电路构成并有数字显示特点的一种现代计数器,与传统的机械计时器相比,它具有走时准、显示直观、无机械磨损等,因而广泛应用于车站、码头、商店等公共场所。目前,数字电子钟的设计,主要是采用计数器等集成电路构成,由于所用集成电路多。连线杂乱,不便阅读。本文采用层次电路设计,将各单元电路设计成层次电路,这样每个单元电路和整体电路连线一目了然,既美观也便于阅读,还有利于团队设计,因每一层次电路为一独立电路,便于独立设计和修改。

1 设计任务

(1)电子钟能显示"时"、"分"、"秒";

(2)能够实现对"时"、"分"、"秒"的校时。

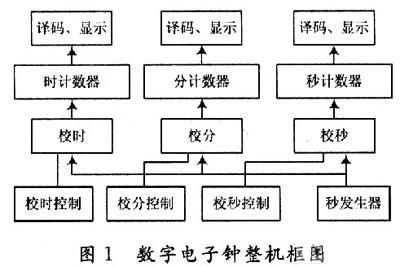

2 整机框图

数字电子钟主要由秒信号发生器、"时、分、秒"计数器、译码显示器、校时电路等组成。秒信号发生器主要由石英晶体振荡器或555振荡器分频后得到;秒、分都是60进制,故由60进制计数器构成;时为24进制,即由24进制计数器构成;显示部分由译码和数码显示构成;校时电路由门电路和开关等构成。整机框图如图1所示。

3 各部分电路设计

3.1 秒、分、时计数器

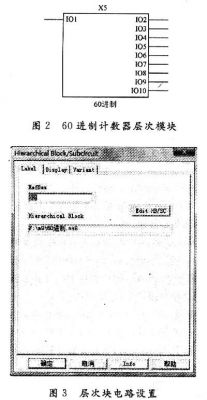

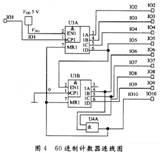

秒、分计数采用60进制计数器,时采用24进制计数器。它们都是8个BCD码输出,1个进位输出,1个时钟脉冲输入。在设计层次电路时,皆可设计为1个输入端,9个输出端。在Multisim仿真软件中,执行Place/New Hierachical Block命令,在fiIe name of Hierachical Block中填入你要设计的电路名称,如"60进制计数器"等,再根据需要在输入、输出端口数中填写所需数字,点"OK"后,即得如图2所示电路层次模块。双击它,得到图3所示窗口,点Edit HB/SC对其内电路进行设计。若要进行修改,同样采用以上步骤。

由此,采用4518十进制计数器,设计了60进制和24进制的计数器,计数器的内部电路分别如图4、图5所示。

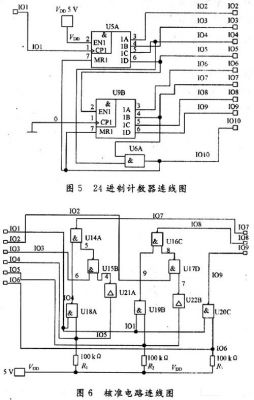

3.2 校准电路

同样的方法,设计校准电路的层次电路时,设计为6个输入口、3个输出口,其内部电路如图6所示。为便于使用,将校准开关外接。

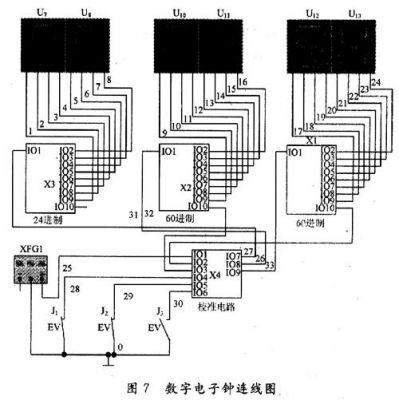

校时电路工作过程如图7所示,正常工作情况下,J3断开,J1,J2闭合,秒脉冲进入计数器。当需要对秒进行校正时,闭合和断开J3,直到需要的数字为止;需要对分校正时,J3处于闭合的情况下,断开J2,秒脉冲进入到分计时,则分计数器快速计数,直到显示的时间为需要的数字为止,再闭合J2;同理,可以对时进行校正。

4 整机电路安装调试

在Multisim中,执行Place/Hierachical Block命令,找到已存储的层次块,点打开即可出现在电路模扳中,再在元件库中找出信号发生器和数码显示器。本例中采用现成的信号发生器,可以将信号频率设置为较高频率,以便快速调节。数码显示器直接采用16位数码显示管,因本例中不会出现大于9的数码,即使初始可能出现,可以通过校时电路快速调节为所需数字。

为使各电路接线后能顺利工作,对各层次块可以先分别测试其功能。将信号发生器分别接入60进制和24进制计数器层次块,其输出接数码管或示波器看其是否能完成其功能。对其校准电路,只有当整机电路接好后,按校准电路所说工作方式,看是否能起到时、分、秒的校准。本例中各模块皆能完成其功能,接好整机电路后,能完成所需功能,故本例数字电子钟满足设计任务。

5 结语

采用层次电路设计方法,对数字电子钟进行了设计,较好地完成了该电路的设计任务。整机电路连线美观,各部分电路功能明确,便于理解整体电路的构成、工作原理等。在数字电路及其他更多的课程中都涉及到较复杂的电路设计,若是采用层次电路设计方法,既便于对电路的理解,也便于团队协作,共同完成设计任务,故而层次电路设计方法将会广泛地应用在大型复杂电,路系统的设计中。

- Multisim10在差动放大电路分析中的应用(01-18)

- 基于Multisim 8的弱信号放大电路的仿真测试(05-19)

- 直耦式宽频带功率放大器的设计与调试(12-28)

- 基于Multisim的负电阻特性分析及应用(07-26)

- 基于Multisim 10的差动放大电路仿真分析(08-31)

- 基于Multisim7的负反馈放大电路的研究(12-01)