无源UHF RFID标签的低成本阻抗匹配网络设计

La=1512nH。

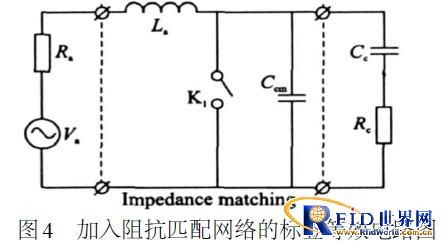

开关K1断开时,芯片处于状态0。在图5所示的从标签芯片输入阻抗到天线的共轭阻抗的匹配路径上,点1处阻抗为22-j106欧;并联电容Ccm后与158等电阻圆交于点2,阻抗为15-j888;再串联电感La到达点3,其阻抗为158,与修正过后的天线阻抗Ra共轭匹配。经计算可以得到Ccm=340fF。

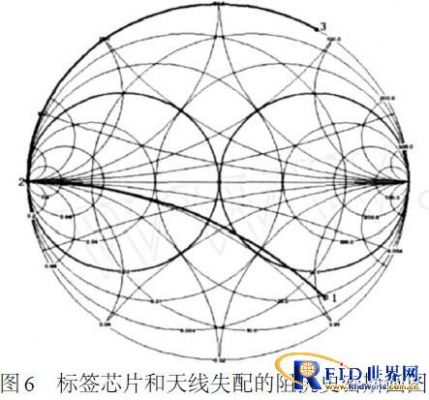

天线和芯片接口处没有复功率波反射,芯片和天线的共轭匹配使天线将从空中接收到的射频能量的一半传递给芯片,达到功率传输的最大化。开关K1闭合时,芯片处于状态1。图6所示为标签芯片输入阻抗变化的路径。

2.1.2 性能比较

在未进行阻抗匹配的情况下,芯片Qc的值为4182;加入阻抗匹配网络后,在芯片和天线阻抗共轭匹配状态下,Qc增大到5187,由公式(3)可得芯片获得的交流电压Vc增大到原来的111倍,改善了芯片的性能。

通过比较可知,本芯片的矢量微分RCS的模值要大1015dB,大大改善了标签反射信号的可识别性,提高了读写器对标签识别的准确率。

2.1.3 电路实现

阻抗匹配网络由电容Ccm和开关K1两部分组成,如图7所示。为了保证两个天线引脚间电路的对称,Ccm采用两个电容并联的形式,每个大小为170fF;K1由两个PMOS开关管组成,PMOS由基带信号经过电平转换电路(图7中A部分)后驱动,因此PMOS的栅极可以获得更高的栅压,保证关断状态可靠截止;B部分为上电保护电路,保证数字基带给出的上电复位信号处在稳定状态下芯片才能进入调制反射,避免了由于数字基带电路复位前状态不确定而导致芯片在无法获得工作能量的情况下反射。PMOS开关管和NMOS上电保护管均采用网状栅极结构,增大MOS管的宽长比,有利于减小MOS管的电阻和寄生电容。

3 测试结果

所设计的RFID标签芯片基于chartered0135Lm2P4M、低阈值CMOS工艺流片,芯片尺寸1026Lm×1796Lm,图8为芯片的显微照片。实际使用过程中,芯片仅有两个引脚与天线相连,图中所显示的其余引脚均为测试所用,连接对应的模拟或数字信号。

倍压电路的输出电平是决定RFID芯片工作性能的重要指标,采用本阻抗匹配电路的芯片在输入交流电平仅为300mV时,输出直流电平可达1147V,完全满足芯片正常工作所需电平要求。1800026C中规定的RFID工作频带为860~960MHz,与我国的规定[11]在920~925MHz频段相重合,因此所设计的RFID标签工作在923MHz频带。

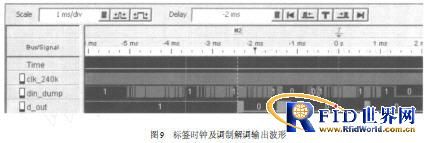

使用Impinj公司的speedway读写器,设置发送功率为2WERP,标签天线增益115dBi,在自由空间中进行测试。使用安捷伦1682A逻辑分析仪测试信号波形如图9,图中“clk-240k”为系统工作时钟,频率为240kHz;“din-dump”为解调输出信号;“d-out”为调制输出信号。测试表明,采用该阻抗匹配网络的标签在和读写器通信的过程中,误码率低于10-4,标签的一次识别更为准确。

4 结论

提出了一种符合ISO1800026C标准的无源RFID标签的低成本的阻抗匹配网络。电路结构简单,在读写器、标签天线和芯片之间实现了功率传输的最大化。采用该阻抗匹配方法的标签芯片已通过chartered0135LmCMOS工艺流片验证。理论分析和实测结果都表明,该方法有效的改善了芯片性能,提高了读写器对标签识别的准确率,标签满足系统设计要求。

- RFID标签测试技术浅析(06-26)

- RFID标签各种测试与测量方法(07-05)

- RFID多标签阅读时防碰撞技术(11-29)

- 纸基RFID包装箱标签天线设计(01-25)

- 基于WiFi和RFID定位技术的电子标签定位算法(01-06)

- 基于FPGA的RFID板级标签设计与实现(12-12)