一种中速高精度模拟电压比较器的设计

时间:02-07

来源:EDN

点击:

1 引言

在A/D转换器中,比较器重要性能指标是工作速度、精度、功耗、输入失调电压、正反馈时产生的回程噪声等,这些指标影响和制约着整个A/D转换器的性能。高速比较器速度较快,一般采用锁存器(Latch)结构,但是失调和回程噪声较大,精度在8位以下,用于闪烁(Flash)、流水线(Pipeline)型等高速A/D转换器。高精度比较器可分辨小电压,但速度相对较慢,一般采用多级结构,且较高的精度决定失调校准的必要性。这里设计的比较器是用于输入范围2.5 V、速度1 MS/s、精度12位的逐次逼近型A/D转换器,为了满足A/D转换器的性能指标,则需采用中速高精度的比较器。

2 比较器的设计

由于该比较器用于输入电压2.5 V、速度1 MS/s、精度12位的逐次逼近型A/D转换器,因此比较器的精度至少应达到1/2 LSB,即0.3 mV的电压,速度高于12 MHz,并且需要考虑一定的设计余量,所以暂定指标为精度O.2 mV、速度20 MHz。该中速高精度的比较器通常采用多级结构实现。在利用锁存器速度高、功耗小等优点的基础上,采用3级前置放大器组成的预放大级提高精度;采用输入失调储存与输出失调储存技术相结合的办法降低甚至抵消失调的影响;采用共源共栅、源随器结构的前置放大器和锁存器的时钟控制来抑制回程噪声的影响;采用数字触发电路获得高性能的数字输出信号。需要注意的是必须准确处理好比较器的各个工作阶段,使其各部分协调工作,降低相互之间的干扰,以达到最优的性能。

2.1 总体结构与失调校准技术

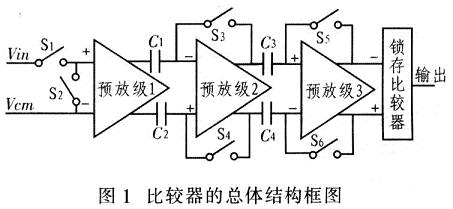

图1为比较器电路的总体结构框图。采用3级电容耦合的前置放大器加锁存比较器的结构,其中耦合电容可用于失调储存,开关用于控制比较器工作。

暂不考虑锁存比较器的时钟控制以及整个电路的复位工作,该比较器工作大致分为2阶段:首先是失调校准阶段,S1断开,S2闭合,使预放级1的正负输入端连接在中间电压Vcm上,同时,S3~S6闭合,这样预放级1的输出失调电压就存储在C1、C2上,预放级2和预放级3的输入失调电压则分别存储于C1、 C2和C3、C4;然后是比较阶段,S1闭合,S2~S6断开,比较器开始比较Vcm和Vin,由于预放级1~3的失调电压绝大部分存储在电容C1~C4 上,因此失调电压相互抵消,同时由于3级前置放大器增益的存在,锁存比较器失调电压的影响也减小相应倍数。

假设预放级1~3和锁存比较器的失调电压分别是Vos1、Vos2、Vos3、VosL,预放级1~3的增益分别为A1、A2、A3,开关S3、S4和 S5、S6注入到电容上的电荷失配量分别为△Q3,4、△Q5,6电容C1~C4的电容量都为C,则使用失调校准技术后,比较器的残余输入失调将为:

从式(1)看出,要达到0.2 mV的分辨率,还应根据锁存器的失调电压确定前置放大器的增益。由于锁存器的失调电压通常不会超过100 mV,因此总增益可确定为500。然后再来考虑增益分配问题。预放级1需要将0.2 mV的小信号输入迅速放大,所以预放级1的带宽要大。在一定增益带宽积的前提下。意味着增益要小,同时预放级1采用输出失调存储的失调校准技术,也要求预放级1增益要小,以避免因放大后的输入失调在电容C1、C2上饱和而达不到消除失调的效果。同时,预放级2、3采用输出失调存储的失调校准技术,输入的信号幅度也较大,因此可采用较大的增益。最终确定预放级1的增益约为5,预放级2、3的增益约为10。

2.2 比较器第一级的结构

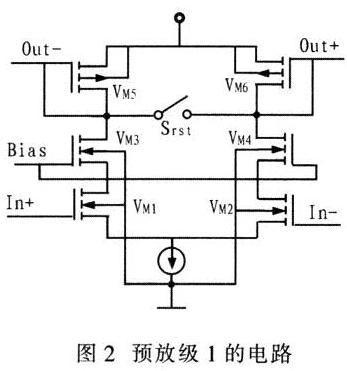

由于第一级前置放大器需将0.2 mV的小信号输入迅速放大,同时采用输出失调存储的失调校准技术,这就要求它具有高带宽和低增益特点。因此,预放级1可以采用二极管连接成PMOS作负载的差分运放结构,同时考虑本级也是整个高精度模拟电压比较器的输入极,它的噪声性能也对比较器的精度有影响,因此输入则采用共源共栅(Cascode)的结构,这可将回程噪声减小gm3,4/gm5,6倍,这在比较器一端固定电位,另一端作输入应用的情况下尤其重要,最后再加入一个源随器作为输出级,既可调节后级放大器的输入直流电平达到最佳值,又可起到隔离的效果改善噪声性能。预放级1的电路如图2所示(后接的源随器未画出)。

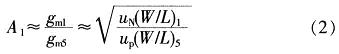

假设电路是完全对称的结构,则整个电路的增益A1约为:

该值一般都在10以下,考虑到带宽要求和电容上失调电压饱和的问题,最终确定其取值约为5。同时,在输出端Out+与Out-之间加入复位开关,在每个比较周期的最初,由复位信号控制开关闭合。将预放级1复位,加快比较速度。

2.3 比较器第

在A/D转换器中,比较器重要性能指标是工作速度、精度、功耗、输入失调电压、正反馈时产生的回程噪声等,这些指标影响和制约着整个A/D转换器的性能。高速比较器速度较快,一般采用锁存器(Latch)结构,但是失调和回程噪声较大,精度在8位以下,用于闪烁(Flash)、流水线(Pipeline)型等高速A/D转换器。高精度比较器可分辨小电压,但速度相对较慢,一般采用多级结构,且较高的精度决定失调校准的必要性。这里设计的比较器是用于输入范围2.5 V、速度1 MS/s、精度12位的逐次逼近型A/D转换器,为了满足A/D转换器的性能指标,则需采用中速高精度的比较器。

2 比较器的设计

由于该比较器用于输入电压2.5 V、速度1 MS/s、精度12位的逐次逼近型A/D转换器,因此比较器的精度至少应达到1/2 LSB,即0.3 mV的电压,速度高于12 MHz,并且需要考虑一定的设计余量,所以暂定指标为精度O.2 mV、速度20 MHz。该中速高精度的比较器通常采用多级结构实现。在利用锁存器速度高、功耗小等优点的基础上,采用3级前置放大器组成的预放大级提高精度;采用输入失调储存与输出失调储存技术相结合的办法降低甚至抵消失调的影响;采用共源共栅、源随器结构的前置放大器和锁存器的时钟控制来抑制回程噪声的影响;采用数字触发电路获得高性能的数字输出信号。需要注意的是必须准确处理好比较器的各个工作阶段,使其各部分协调工作,降低相互之间的干扰,以达到最优的性能。

2.1 总体结构与失调校准技术

图1为比较器电路的总体结构框图。采用3级电容耦合的前置放大器加锁存比较器的结构,其中耦合电容可用于失调储存,开关用于控制比较器工作。

|

暂不考虑锁存比较器的时钟控制以及整个电路的复位工作,该比较器工作大致分为2阶段:首先是失调校准阶段,S1断开,S2闭合,使预放级1的正负输入端连接在中间电压Vcm上,同时,S3~S6闭合,这样预放级1的输出失调电压就存储在C1、C2上,预放级2和预放级3的输入失调电压则分别存储于C1、 C2和C3、C4;然后是比较阶段,S1闭合,S2~S6断开,比较器开始比较Vcm和Vin,由于预放级1~3的失调电压绝大部分存储在电容C1~C4 上,因此失调电压相互抵消,同时由于3级前置放大器增益的存在,锁存比较器失调电压的影响也减小相应倍数。

假设预放级1~3和锁存比较器的失调电压分别是Vos1、Vos2、Vos3、VosL,预放级1~3的增益分别为A1、A2、A3,开关S3、S4和 S5、S6注入到电容上的电荷失配量分别为△Q3,4、△Q5,6电容C1~C4的电容量都为C,则使用失调校准技术后,比较器的残余输入失调将为:

|

从式(1)看出,要达到0.2 mV的分辨率,还应根据锁存器的失调电压确定前置放大器的增益。由于锁存器的失调电压通常不会超过100 mV,因此总增益可确定为500。然后再来考虑增益分配问题。预放级1需要将0.2 mV的小信号输入迅速放大,所以预放级1的带宽要大。在一定增益带宽积的前提下。意味着增益要小,同时预放级1采用输出失调存储的失调校准技术,也要求预放级1增益要小,以避免因放大后的输入失调在电容C1、C2上饱和而达不到消除失调的效果。同时,预放级2、3采用输出失调存储的失调校准技术,输入的信号幅度也较大,因此可采用较大的增益。最终确定预放级1的增益约为5,预放级2、3的增益约为10。

2.2 比较器第一级的结构

由于第一级前置放大器需将0.2 mV的小信号输入迅速放大,同时采用输出失调存储的失调校准技术,这就要求它具有高带宽和低增益特点。因此,预放级1可以采用二极管连接成PMOS作负载的差分运放结构,同时考虑本级也是整个高精度模拟电压比较器的输入极,它的噪声性能也对比较器的精度有影响,因此输入则采用共源共栅(Cascode)的结构,这可将回程噪声减小gm3,4/gm5,6倍,这在比较器一端固定电位,另一端作输入应用的情况下尤其重要,最后再加入一个源随器作为输出级,既可调节后级放大器的输入直流电平达到最佳值,又可起到隔离的效果改善噪声性能。预放级1的电路如图2所示(后接的源随器未画出)。

|

假设电路是完全对称的结构,则整个电路的增益A1约为:

|

该值一般都在10以下,考虑到带宽要求和电容上失调电压饱和的问题,最终确定其取值约为5。同时,在输出端Out+与Out-之间加入复位开关,在每个比较周期的最初,由复位信号控制开关闭合。将预放级1复位,加快比较速度。

2.3 比较器第

- 建立比较器的外部滞回电压(11-28)

- 比较器的合理选择(06-09)

- 采用新型放大器实现高性能的电流检测(05-10)

- 适用于SAR ADC的CMOS比较器的设计(01-02)

- 利用低功耗比较器自动检测音频附件(05-11)

- 高性能CMOS集成电压比较器设计(10-07)