射频识别阅读器中信道选择滤波器的设计

射频识别( RFID)技术在当今无线通信领域应用十分广泛。相对于LF( 120~ 135 kH z)波段和HF( 13. 56MH z) 波段, UHF波段的RFID技术能够在m 级距离上提供数百kb it/s的数据通信, 因而备受关注。目前成功商业应用的UHF 射频识别系统阅读器往往采用分立元件构造, 共同的缺点是体积大、功耗大。随着CMOS工艺技术的发展进步, 如果能够提供基于CMOS工艺的单片阅读器将极大的降低成本, 应用前景也将更为广阔; 而且单片集成的阅读器方案也符合当前多应用便携式终端的发展趋势, 为未来多应用整合提供可能。

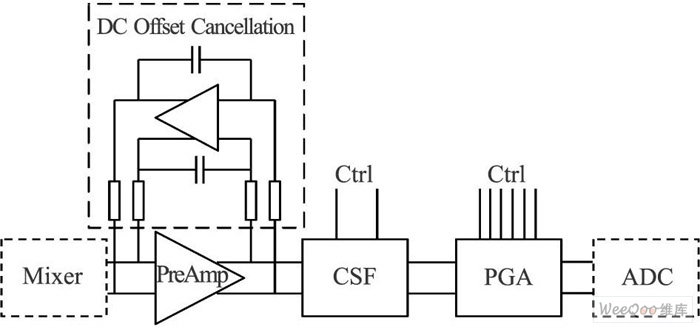

本文设计的信道选择滤波器用于UHF RFID阅读器接收机模拟基带部分, 接收机采用I/Q 两支路正交的零中频结构, 图1是接收机模拟基带结构图。

根据EPC global C1G2协议要求, UHF RF ID阅读器接收的最高数据速率达到640 kb it/s, 最大信号带宽不超过1. 28MH z; 对于40 kbit/s的最低速率, 其信号带宽小于250 kH z, 于是, 接收基带信道选择滤波器的带宽为0. 3~ 1. 3MH z范围内可调。

图1 信道选择滤波器用于RFID模拟基带

另外, 根据transmissiON mask的要求, 相邻两信道的功率差为40 dB。在本信道最小信号条件下,仍要保证本信道与相邻信道同时保持通信, 这就要求信道选择滤波器能够克服临道比本道高40 dB的干扰, 于是在设计的时候要求信道选择滤波器在两倍频处有大于45 dB的抑制。

根据UHF RFID接收机结构的特点, 在多读写器环境中, 接收机将面临幅度较大的干扰信号, 这就要求滤波器有能力处理大幅度的输入信号, 即对其线性度要求较高。为了得到更高的线性度与更好的噪声特性, 设计采用运算放大器- RC 结构滤波器模式。通过仿真, 决定采用六阶Chebyshev低通滤波器结构来实现信道选择滤波器的设计。

文章首先给出了六阶Chebyshev低通滤波器设计过程; 然后给出Chebyshev低通滤波器的版图以及滤波器和运放的仿真结果; 最后做出结论。

1 六阶Chebyshev低通滤波器设计

1. 1 二阶Chebyshev低通滤波节

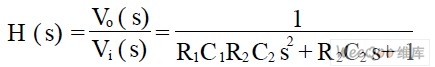

图2给出了其二阶低通滤波节(B iquad)结构,其传递函数为:

尽管带内的平坦特性不如Butterworth近似,但它具有更快的幅度衰减特点。

图2 二阶Chebyshev低通滤波节

从图2可以看到, 滤波器中的运算放大器接成了缓冲器形式, 是典型的双端输入、单端输出的运算放大器。由于缓冲器的两个输入端均悬空, 当输入信号为差分形式时, 无法构成全差分缓冲器[ 7 ]。通常的解决方法是用两个单端输出的运算放大器去实现一个全差分结构的缓冲器, 即一个运放作为正输入端, 另一个运放作为负输入端, 这就造成了器件数量的加倍, 输入端的匹配也很难达到, 所形成的全差分缓冲器的性能并不理想。如何形成全差分的缓冲器, 在运放的设计过程中需要着重考虑。

1. 2 运放的设计

运算放大器是运算放大器- RC 滤波器的核心部件。根据系统的设计要求, 运算放大器开环增益在70 dB以上, 增益带宽积大于65 MH z, 相位裕度取在65b~ 70b左右, SR值应取大于12 V /L s。上文中提出缓冲器输入端悬空的问题, 采用全平衡差动放大器FBDDA( Fu lly BalancedD ifferentia lDifferenceAmplifier)可以方便的解决。

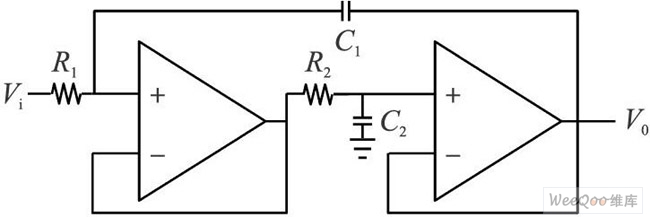

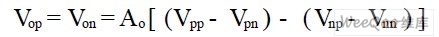

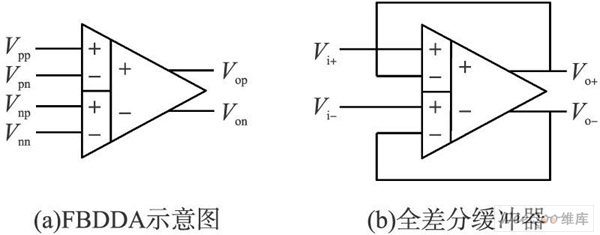

图3给出了FBDDA的示意图及按照负反馈方式构成的全差分缓冲器结构。FBDDA的输入输出关系可以表示为:

Ao 为理想状态下运放的开环增益。当采用负反馈时可以得到如下的关系:

以上关系仅当Aoy ] 时才可以成立, 所以在设计运放时开环增益越大越好。

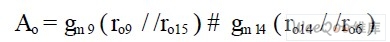

图3 FBDDA 与全差分缓冲器

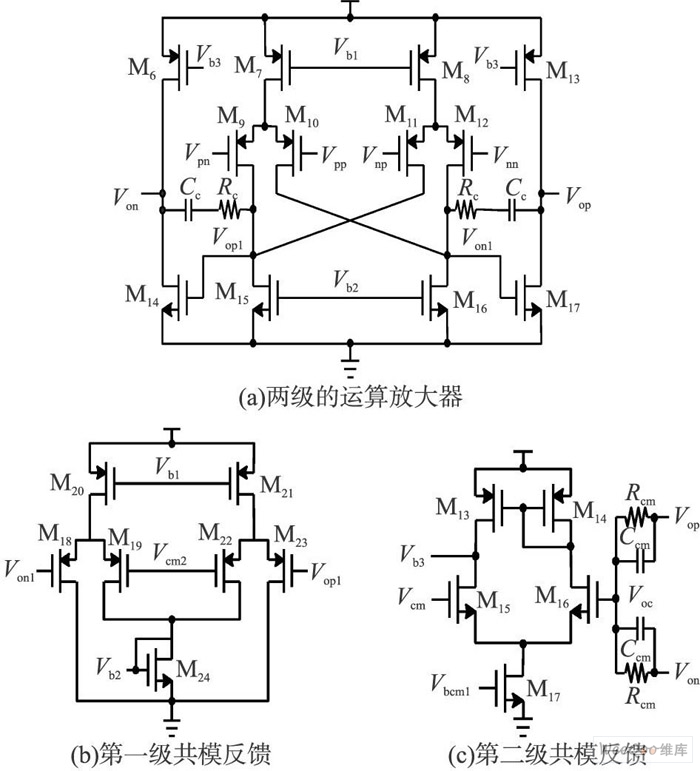

图4所示为FBDDA。图4( a)是一种两级结构的运算放大器, 是FBDDA的核心电路, 图4( b)与图4( c)所示电路分别用来稳定运算放大器第一级输出与第二级输出的共模电平。运算放大器的第一级放大器由两个差分对构成, 使得电路具有四个输入端。为了获得良好的噪声系数, 电路的输入管为PMOS管(M9、M10、M11、M12 ), 负载管为NMOS 管(M15、M16 )。运算放大器的第二级为共源级结构,输入管采用NMOS管(M14、M17 ), 负载管采用PMOS管(M6、M18 )。电路采用米勒补偿电容(Cc )和调零电阻(Rc )以保证运放的闭环稳定性。经过计算可以得到全平衡差动电路的小信号增益如下式所示:

图4 全差分差动放大器电路

其中gm 和ro 分别表示MOS管的跨导和输出电阻。

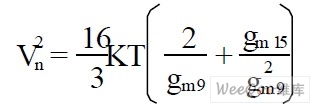

为了提高运放的增益, 可以增大gm 和ro。经过计算放大器的等效输入热噪声可表示为:

其中K为波耳兹曼常数( 1. 38 @10-23J/K), T 为开尔文温度。从上式可以看出, 要减小整个运放的噪声,输入管应使用较大宽长比的PMOS管, 负载管应使用较小宽长比的NMOS管。一般