如何利用电容式数字隔离器进行设计

时间:01-19

来源:EDN

点击:

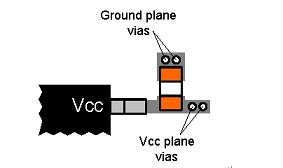

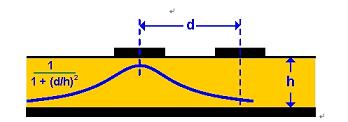

图 5 利用 d = 3h 来最小化串扰 使用45o走线弯曲(或者斜切式弯曲)而非90o弯曲,可保持有效的走线阻抗并避免信号反射。为了实现在噪声环境下的工作,将隔离器的闲置启动输入通过一个电阻器(1kΩ到10kΩ)连接到合适的参考层。将高电平有效、高位允许输入连接到电源层,同时将低电平有效输入连接至接地层。 当过孔电感增加信号路径电感时,要避免各层随快速信号走线改变。 在隔离器与周围电路之间使用较短的走线长度可避免噪声引入。数字隔离器通常会带有隔离式DC/DC转换器,后者提供了跨越隔离层的电源。由于隔离器的单端传输信号对噪声引入过于敏感,因此邻近DC/DC转换器的开关噪声可以很容易被长信号走线引入。 将大容量电容(比如10μF)置于靠近电源如稳压器旁,或是在电源进入PCB的地方。 通过将电容的电源端直接连接至器件的电源端,然后经过孔连至Vcc层,在器件上安装小容量的0.1μF或0.01μF旁路电容。经数个过孔将电容接地端连接至接地层(请参见图6)。

|

- 基于电容检测芯片的电容检测系统设计(07-28)

- 基于CAV424的电容式压力传感器测量电路设计(08-21)

- 如何开发性能优异的电容式触摸屏(11-17)

- 触摸产品的关键参数解析(12-09)

- 投射电容屏内部噪声消除措施(06-06)

- 三轴加速度传感器介绍(09-27)