如何选择电容器实现高性能的EMI滤波

时间:10-28

来源:AVX 公司 Jeffrey Cain and Steve Makl

点击:

长期以来,一直使用旁路和去耦电容来减小PCB上产生的各种噪声,也。由于成本相对较低,使用容易,还有一系列的量值可选用,电容器常常是电路板上用来减小电磁干扰(EMI)的主要器件。由于寄生参数具有重要的影响,故电容器的选择要比其容量的选择更为重要。制造电容器的方法很多,制造工艺决定了寄生参数的大小。

电气器噪声可以以许多不同的方式引起。在数字电路中,这些噪声主要由开关式集成电路,电源和调整器所产生,而在射频电路中则主要由振荡器以及放大电路产生。无论是电源和地平面上,还是信号线自身上的这些干扰都将会对系统的工作形成影响,另外还会产生辐射。

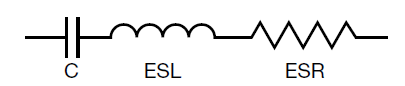

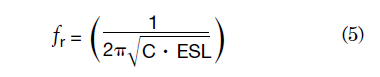

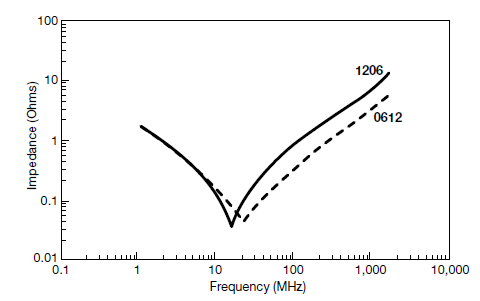

本文将重点讨论多层陶瓷电容器,包括表面贴装和引脚两种类型。讨论如何计算这些简单器件的阻抗和插入损耗之间的相互关系。文中还介绍了一些改进型规格的测试,如引线电感和低频电感,另外,还给出了等效电路模型。这些模型都是根据测得的数据导出的,还介绍了相关的测试技术。针对不同的制造工艺,测试了这些寄生参数,并绘制出了相应的阻抗曲线。

阻抗和插入损耗

所幸的是,电容器还算简单的器件。由于电容器是一个双端口器件,故仅有一种方法与传输线并接。不要将该器件看作一只电容器,更容易的方法是将其看作为一个阻抗模块。当其与传输线并联时,甚至可以将其视作为一个导纳模块(见图1)。

电气器噪声可以以许多不同的方式引起。在数字电路中,这些噪声主要由开关式集成电路,电源和调整器所产生,而在射频电路中则主要由振荡器以及放大电路产生。无论是电源和地平面上,还是信号线自身上的这些干扰都将会对系统的工作形成影响,另外还会产生辐射。

本文将重点讨论多层陶瓷电容器,包括表面贴装和引脚两种类型。讨论如何计算这些简单器件的阻抗和插入损耗之间的相互关系。文中还介绍了一些改进型规格的测试,如引线电感和低频电感,另外,还给出了等效电路模型。这些模型都是根据测得的数据导出的,还介绍了相关的测试技术。针对不同的制造工艺,测试了这些寄生参数,并绘制出了相应的阻抗曲线。

阻抗和插入损耗

所幸的是,电容器还算简单的器件。由于电容器是一个双端口器件,故仅有一种方法与传输线并接。不要将该器件看作一只电容器,更容易的方法是将其看作为一个阻抗模块。当其与传输线并联时,甚至可以将其视作为一个导纳模块(见图1)。

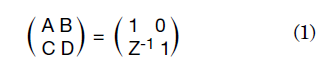

图1:将电容器视作为阻抗模块。 这种连接方式的ABCD参数可以表示为:

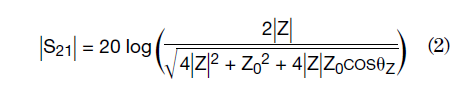

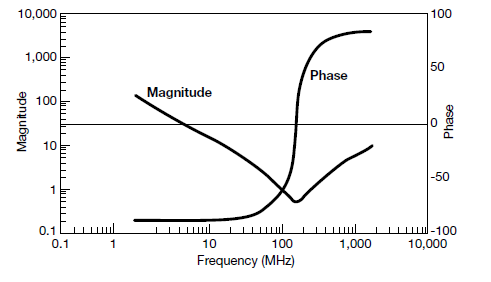

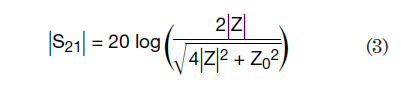

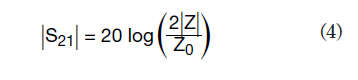

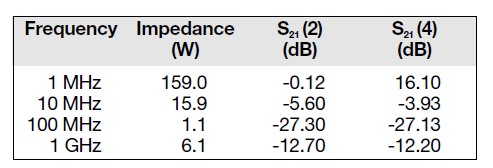

Z0=传输线阻抗 ??=阻抗模块的相角 有一些插入点可以来观察方程2。首先,对于一个高性能的陶瓷电容器来说,其相角在整个频段中都非常接近±90°,只有谐振点附近除外(见图2)。

|

- 输出电容器的等效串联电阻对滞环控制功率转换器的影响(07-12)

- 八种常用电容器的结构和特点(07-04)

- 低压电解电容器的发展趋势(09-14)

- 电容器故障与检测(01-12)

- 超级电容器太阳能草坪灯的设计与实现(02-12)

- 用薄膜电容器替代铝电解电容器的分析与实践(04-20)