基于AD7543和FPGA的数/模转换电路设计

时间:10-19

来源:EDN

点击:

|

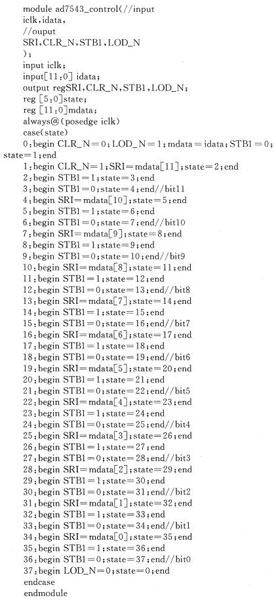

4 FPGA时序模块仿真

为了进一步的验证FPGA控制器模块的正确性,在下载到目标器件之前,可以对此模块进行时序仿真。在工程文件中,首先要新建一个以vwf结尾的波形文件。在弹出的对话框中添加要观察的引脚,然后再设定时钟相关参数和保存波形文件,最后在编译顶层文件之后,可对此模块进行仿真。如图4为FPGA控制器模块仿真波形,CLOCK为此模块的工作时钟,时间周期设为40 ns;ida为并行输入数据,STI为串行输出,STB1为选通脉冲信号。由图可知,STB1的上升沿把STI引脚上的数据装入寄存器A中,装满寄存器A后,LOD设为低电平,把寄存器A的内容装入寄存器B中。仿真时序与图1的时序一致,满足设计要求。

|

5 结 语

针对采用软件控制AD7543数/模转换芯片所具有的缺点的基础上,采用硬件(FPGA)直接对AD7543转换芯片进行控制的方式来设计数/模转换电路,给出具体的硬件实现电路和控制器的Verilog HDL实现代码。因为FPGA控制器是一个独立单元,它几乎不需要CPU的干预就能工作,在电路中分担了CPU的工作量,这不仅提高CPU实时处理信号能力,还会提高系统的可靠性,具有一定的实用价值与参考价值。在此设计了基于FPGA与AD7543转换芯片的数/模转换电路,AD7543的工作时序全部用FPGA器件产生,提高系统的可靠性。

- AD7543与89C2051实现串行接口的设计(04-18)

- 电源管理总线的结构与优势(11-19)

- 新型灌封式6A至12A DC-DC μModule稳压器系列(11-19)

- 低电压PLD/FPGA的供电设计(01-24)

- 基于FPGA的高精度数字电源(02-12)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)