高性能CMOS集成电压比较器设计

时间:10-07

来源:EDN

点击:

|

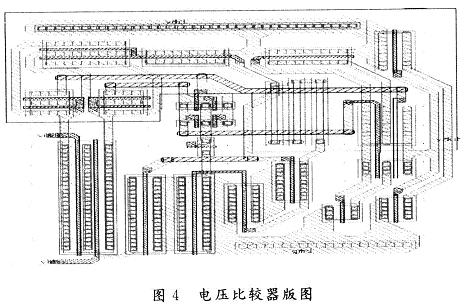

4 结 语

在CSMC O.5μm CMOS工艺条件下,采用预放大器、锁存比较电路和输出缓冲级级联的锁存比较电路结构,设计了一个高速、高精度的高性能集成电压比较器,它具有低输入失调电压、低功耗的特点。完成从电路原理图设计到版图设计和验证(DRC,LVS)以及工艺角仿真和分析的整个设计流程。从仿真结果可以看出,这一高性能电压比较器适用于高速A/D转换器、高速数据传输器及高性能切换功率调节器等设备中。

- 德州仪器高性能模拟运放产品系列介绍集锦(11-13)

- CMOS求和比较器在PWM开关电源控制中的应用(11-27)

- 如何将CMOS LDO应用于便携式产品中(01-15)

- 2.5 Gb/s 0.35μmCMOS光接收机前置放大器设计(01-22)

- 用于下一代移动电话的电源管理划分(08-28)

- 不同电源供电的器件间的桥接(04-27)