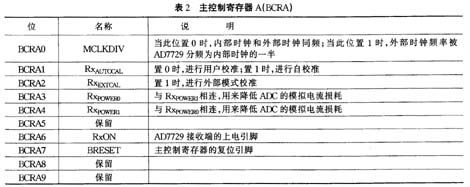

带辅助DAC的双路Σ-Δ转换器的原理及应用

时间:09-01

来源:与非网

点击:

|

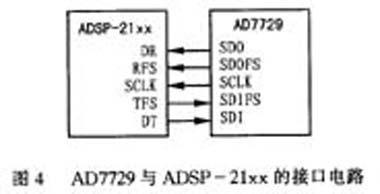

4.接口举例

AD7729还为用户提供了与DSP兼容的标准串行端口,由ADC的串行时钟控制串行数据和I/O DSP信息。

图4为AD7729与ADI公司的ADSP-21xx的接口原理图。对于ADSP-21xx,串行端口的控制寄存器必须设置为TFSR=RFSR=1 (保证每个转换器的帧同步),SLEN=15(16位字长),TFSW=RFSW=0(正常帧同步),INVIFS=INVRFS=0(高有效的帧同步信号),IRFS=0(外部RFS),ITFS=1(内部TFS)和ISCLK=0(外部串行时钟)。

|

AD7729是一种带辅助DAC的双路Σ-Δ模数转换器,它不仅具有噪音低,精度高,工作速度快等优点,并且可与多种DSP接口,通用性很强。所以该器件是新一代理想的数据采集和模数转换器件,可广泛应用于通讯、多媒体和高性能仪器中。

DAC Σ-Δ模数转换器 CMOS AFC 串行端口 相关文章:

- 德州仪器高性能模拟运放产品系列介绍集锦(11-13)

- 如何使低功耗放大器在便携式产品中提高性能(10-03)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 高速DAC AD9712B/AD9713B的原理和应用(11-30)

- 混频器用作开关,可使 DAC 采样频率加倍(01-22)

- 什么是DAC(数模转换器)(01-24)