外部电源设计中新技术与芯片的应用

时间:07-30

来源:EDN

点击:

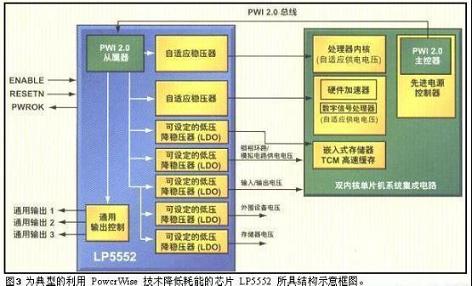

其技术参数如下:LP5552输出数目为7;输出电压及电流有:2个降压稳压器为0.8v到1.235v输出电压,800mA的输出电流;5个降压稳压器为0.8v到3.3v输出电压,高达250mA的输出电流。输入电压范围为2.7V至4.8V。接口为PWl 2.0。封装为micro SMD-38。

4.3 Power Wise技术应用

Power Wise®技术是先进的能源管理解决方案,主要针对当前和未来受能源所限制的数字设备,适用于双内核处理器、手机、便携式收音机、个人数字助理、以电池供电的电子产品以及便携式设备。可将数字处理器的能耗降低70%,从而延长电池寿命、支持更多功能和改善使用者的体验。Power Wise采用自适应电压调节(AVS)和阈值电压调节等技术,将数字逻辑集成电路的工作和泄漏功耗自动降至最低,同时保持最小的系统开销。

Power Wise技术提供在单芯片系统和支持组件之间的一种优化的闭环回路,而无需CPU干涉。嵌入式Power Wise技术因为可以合成,所以可不受处理器影响。

5 结束语--电源排序技术也是一种较为理想之节能方案

除上述选择节能芯片和利用智能电源管理技术节省能源二个方面之外,需指出的是对于不同类型的产品其节能技术方式也有所不同。而电源排序技术的应用也是一种较为理想之方案。因为在很多大功率系统中,空间和冷却系统的成本都很高。因此,就任何POL转换器而言,做到紧凑、高效率并具有低静态电流以满足新的"绿色"标准都是极端重要的。另外,很多微处理器和数字信号处理器(DSP)都需要一个内核电源和一个输入/输出(1/O)电源,这些电源在启动时必须排序。设计人员必须考虑加电和断电操作时内核和I/O电压源的相对电压和时序,以符合制造商的性能规格要求。没有恰当的电源排序,就可能出现闭锁或过大的电流消耗,这有可能导致微处理器I/O端口损坏,或存储器、可编程逻辑器件(PLD)、现场可编程门阵列(FPGA)、数据转换器等支持性器件的I/O端口损坏。